# 2015•2016

# Masterproef Evaluation of CAESAR candidates on FPGA

Promotor : Prof. dr. ir. Nele MENTENS

Jasper Gorissen

wetenschappen: elektronica-ICT

Promotor : dr. BEGÜL BILGIN

Gezamenlijke opleiding Universiteit Hasselt en KU Leuven

# FACULTEIT INDUSTRIËLE INGENIEURSWETENSCHAPPEN master in de industriële wetenschappen: elektronica-ICT

Copromotor : Dhr. BOHAN YANG Dhr. DANILO SIJACIC

Scriptie ingediend tot het behalen van de graad van master in de industriële

## 2015•2016 Faculteit Industriële ingenieurswetenschappen master in de industriële wetenschappen: elektronica-ICT

# Masterproef Evaluation of CAESAR candidates on FPGA

Promotor : Prof. dr. ir. Nele MENTENS

Promotor : dr. BEGÜL BILGIN Copromotor : Dhr. BOHAN YANG Dhr. DANILO SIJACIC

Jasper Gorissen

Scriptie ingediend tot het behalen van de graad van master in de industriële wetenschappen: elektronica-ICT

## Acknowledgements

First off all, I would like to express my greatest appreciation to all my supervisors, Prof. dr. Ir. Nele Mentens, dr. Begül Bilgin, Mr. Bohan Yang and Mr. Danilo Šijačić, for their encouragement, great advice and enthusiasm in guiding me in the course of this thesis. Prof. dr. Ir. Mentens initial advice helped me get started, and her continued help on some of the more difficult mathematical equations helped me overcome many problems. Dr. Bilgin and Mr. Yang both helped immensely in understanding the authenticated encryption algorithms and more than once offered vital advice when I was stuck. They were always available for questions and also offered many remarks on the thesis, which helped to improve it. Mr. Šijačić offered a great and patient step by step tutorial on the Design compiler, which allowed me to write a script to automate the generation of results. He also gave great advice on this thesis and on the choice of comparison metrics.

I would also like to thank my mother and her friend. They supported my decisions and provided me with everything to get me where I am now. I also would like to thank my brother, friends, and close family for their support. A special thanks also goes out to my girlfriend, who kept my motivation high, and who helped even when she had little time.

## Table of contents

| Acknowledgements                                                                      | i                      |

|---------------------------------------------------------------------------------------|------------------------|

| List of tables                                                                        | v                      |

| List of figures                                                                       | vii                    |

| List of equations                                                                     | ix                     |

| List of graphs                                                                        | xi                     |

| List of abbreviations                                                                 | xiii                   |

| Abstract (Nederlands)                                                                 | xv                     |

| Abstract                                                                              | xvii                   |

| List of equations<br>List of graphs<br>List of abbreviations<br>Abstract (Nederlands) | ix<br>xi<br>xiii<br>xv |

| 1 | Introduct | ion 1                    | l |

|---|-----------|--------------------------|---|

| 2 | Materials | s and methods            | 3 |

|   | 2.1 Aut   | henticated encryption    | 3 |

|   | 2.2 Use   | d programs               | 5 |

|   | 2.2.1     | Xilinx ISE WebPACK       | 5 |

|   | 2.2.2     | AEAD API                 | 5 |

|   | 2.2.3     | ATHENa & Design Compiler | ) |

| 3 | Trivia-ck |                          | l |

|   | 3.1 Alg   | orithm1                  | l |

|   | 3.1.1     | Trivia –SC               | 2 |

|   | 3.1.2     | VPV-Hash                 | 3 |

|   | 3.2 VH    | DL code                  | 1 |

|   | 3.2.1     | Top level block          | 1 |

|   | 3.2.2     | Data Path                | 5 |

|   | 3.2.3     | Finite State Machine     | 7 |

|   | 3.3 Triv  | ria-ck optimisation      | 3 |

|   | 3.3.1     | Basic code               | ) |

|   | 3.3.2     | Area optimisations       | ) |

|   | 3.3.3     | Speed optimisations      | 3 |

|   | 3.3.4     | Trivia-ck version 2      | 5 |

|   | 3.3.5     | Results                  | 5 |

| 4 | Ketje     |                          | 3 |

|   | 4.1 Algo  | orithm                   | 3 |

|   | 4.1.1     | Sponge construction      | 3 |

|   | 4.1.2     | MonkeyWrap construction  |   |

|   |           | ii                       | i |

| MonkeyDuplex construction   |

|-----------------------------|

| KECCAK-p permutation        |

| 40 HDL code                 |

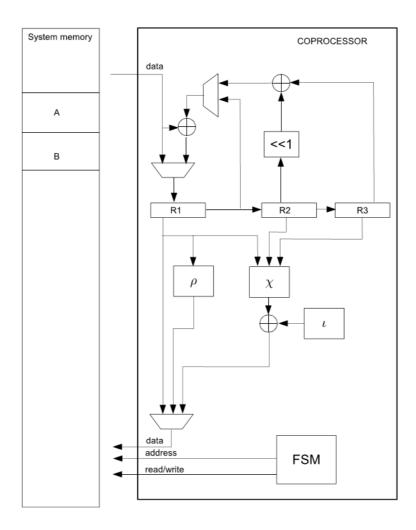

| Data path                   |

| State machine               |

| tje optimisation            |

| Area optimisation           |

| Speed optimisation          |

| State machine optimisations |

| Results                     |

| S                           |

| gorithm                     |

| State update                |

| +DL code                    |

| Data path                   |

| State machine               |

| ORUS optimisation           |

| Results                     |

| nance comparison            |

| sion & discussion           |

|                             |

|                             |

| Literature | 71 |

|------------|----|

| Appendix   | 73 |

## List of tables

| Table 2-1: CAESAR candidates                                                                | 4    |

|---------------------------------------------------------------------------------------------|------|

| Table 3-1: Estimated gate counts of 1-bit to 64-bit hardware implementations [18]           | . 12 |

| Table 3-2: Area results for basic Trivia-ck using AEAD wrapper                              | . 26 |

| Table 3-3: Area usage for basic Trivia-ck without AEAD wrapper                              | . 26 |

| Table 3-4: Area results for area optimised Trivia-ck                                        | . 27 |

| Table 3-5: Area results for speed optimised Trivia-ck                                       | . 27 |

| Table 3-6: Area results for Trivia-ck v2                                                    | . 27 |

| Table 3-7: Timing results for basic Trivia-ck                                               | . 27 |

| Table 3-8: Timing results for area optimised Trivia-ck                                      | . 28 |

| Table 3-9: Timing results for speed optimised Trivia-ck                                     | . 28 |

| Table 3-10: Timing results for Trivia-ck v2                                                 | . 28 |

| Table 3-11: ASIC results for basic Trivia-ck code                                           | . 31 |

| Table 3-12: ASIC results for Trivia_ck area optimisation                                    | . 31 |

| Table 3-13: ASIC results for Trivia_ck speed optimisation                                   | . 31 |

| Table 3-14: ASIC results for Trivia_ck v2                                                   | . 31 |

| Table 4-1: Ketje parameters                                                                 | . 33 |

| Table 4-2: Rho offsets [24]                                                                 | . 38 |

| Table 4-3: Round constants for each of the modes in MonkeyDuplex                            | . 40 |

| Table 4-4: Area results for speed optimised KetjeJr without/with optimised state machine    | . 51 |

| Table 4-5: Area results for area optimised KetjeJr without/with optimised state machine     | . 51 |

| Table 4-6: Area results for speed optimised KetjeSr without/with optimised state machine    | . 51 |

| Table 4-7: Area results for area optimised KetjeSr with optimised state machine             | . 51 |

| Table 4-8: Timing results for speed optimised KetjeJr without/with optimised state machine  | . 52 |

| Table 4-9: Timing results for area optimised KetjeJr without/with optimised state machine   | . 52 |

| Table 4-10: Timing results for speed optimised KetjeSr without/with optimised state machine | . 52 |

| Table 4-11: Timing results for area optimised KetjeSr with optimised state machine          | . 52 |

| Table 4-12: Latency results for Ketje                                                       | . 53 |

| Table 4-13: ASIC results for Ketje implementations with optimised state machine             | . 54 |

| Table 5-1: MORUS parameters [26]                                                            |      |

| Table 5-2: Rotation constants of MORUS [26]                                                 | . 57 |

| Table 5-3: Shift constants of MORUS [26]                                                    | . 57 |

| Table 5-4: Area results for MORUS-640.                                                      |      |

| Table 5-5: Area results for MORUS-1280.                                                     | . 62 |

| Table 5-6: Timing results for MORUS-640                                                     | . 63 |

| Table 5-7: Timing results for MORUS-1280                                                    | . 63 |

| Table 5-8: ASIC results for MORUS implementations                                           | . 63 |

| Table 6-1: Results for minimum area                                                         | . 65 |

| Table 6-2: Results for maximum speed                                                        |      |

| Table 6-3: Throughput/ area results for both optimisation paths                             | . 66 |

| Table 6-4: CAESAR results implemented with the AEAD core on Virtex 6 [29]                   | . 67 |

# List of figures

| Figure 2-1: EtM, E&M, MtE [11]                                                 |      |

|--------------------------------------------------------------------------------|------|

| Figure 2-2: Generic stream cipher [13]                                         | 4    |

| Figure 2-3: The sponge construction [14]                                       | 5    |

| Figure 2-4: An ISim testbench output                                           | 5    |

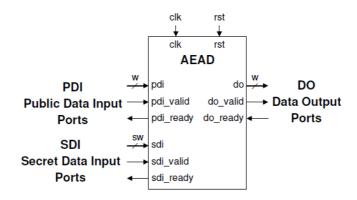

| Figure 2-5: AEAD interface [15]                                                | 6    |

| Figure 2-6: Two formats for SDI [15]                                           | 7    |

| Figure 2-7: Formats for PDI [15]                                               | 7    |

| Figure 2-8: The segment header [15]                                            | 8    |

| Figure 2-9: The AEAD interface [15]                                            | 8    |

| Figure 3-1: Trivia-ck circuit [17]                                             | . 11 |

| Figure 3-2: The Trivia-SC cipherstream and the Trivium cipherstream [17], [19] | . 13 |

| Figure 3-3: Trivia-ck ciphercore                                               | . 15 |

| Figure 3-4: Trivia-ck data path                                                | . 15 |

| Figure 3-5: VPVhash [17]                                                       | . 16 |

| Figure 3-6: Field multiplier                                                   | . 17 |

| Figure 3-7: Trivia state machine                                               | . 18 |

| Figure 3-8: Testbench results from the basic Trivia-ck version                 | . 19 |

| Figure 3-9: A 4:1 mux using 2 LUT's [20]                                       | . 20 |

| Figure 3-10: state machine for the area optimisation                           | . 22 |

| Figure 3-11: Pipelined field multiplier                                        | . 23 |

| Figure 3-12: state machine of the speed optimised code                         | . 25 |

| Figure 4-1: The sponge construction [14]                                       | . 33 |

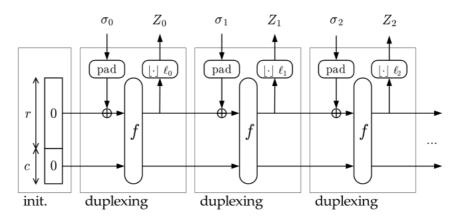

| Figure 4-2 : Duplex construction [14]                                          | . 34 |

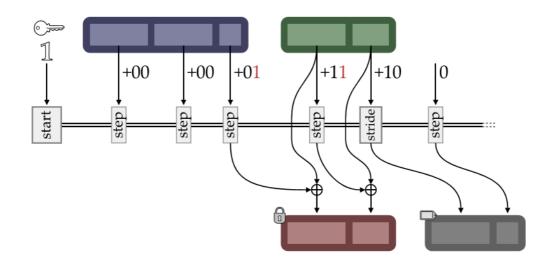

| Figure 4-3: Encrypting data using MonkeyWrap [23]                              | . 35 |

| Figure 4-4: The MonkeyDuplex construction [23]                                 | . 36 |

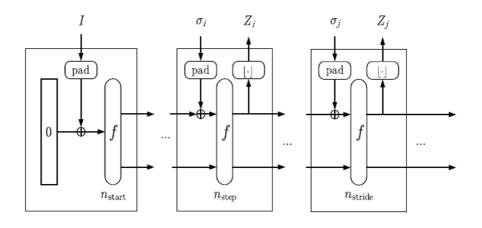

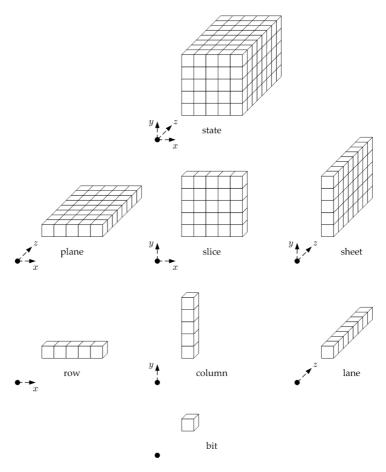

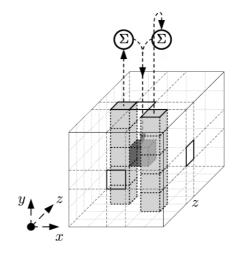

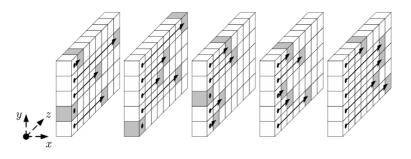

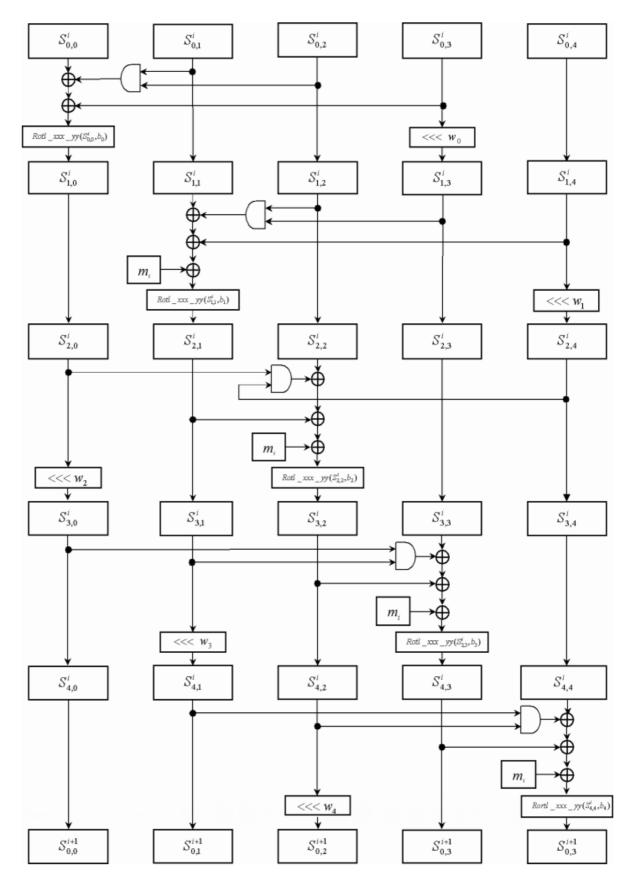

| Figure 4-5: Naming conventions for the KECCAK state [24]                       | . 37 |

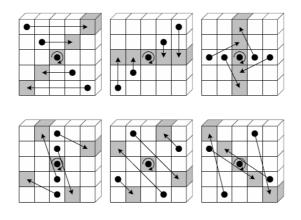

| Figure 4-6: Theta [24]                                                         | . 37 |

| Figure 4-7: The rho step [24]                                                  | . 38 |

| Figure 4-8: The pi step [24]                                                   | . 39 |

| Figure 4-9: The chi step [24]                                                  | . 39 |

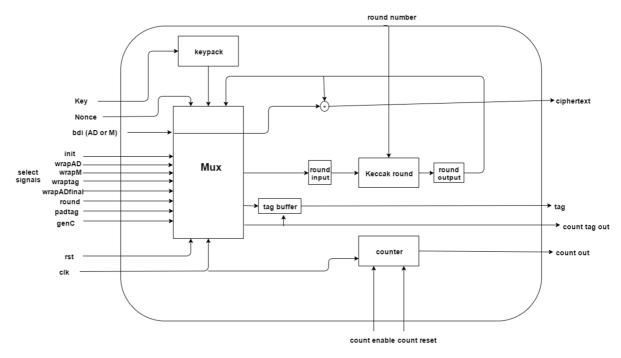

| Figure 4-10: Ketje data path                                                   | . 41 |

| Figure 4-11: Area optimised KECCAK round block [25]                            | . 43 |

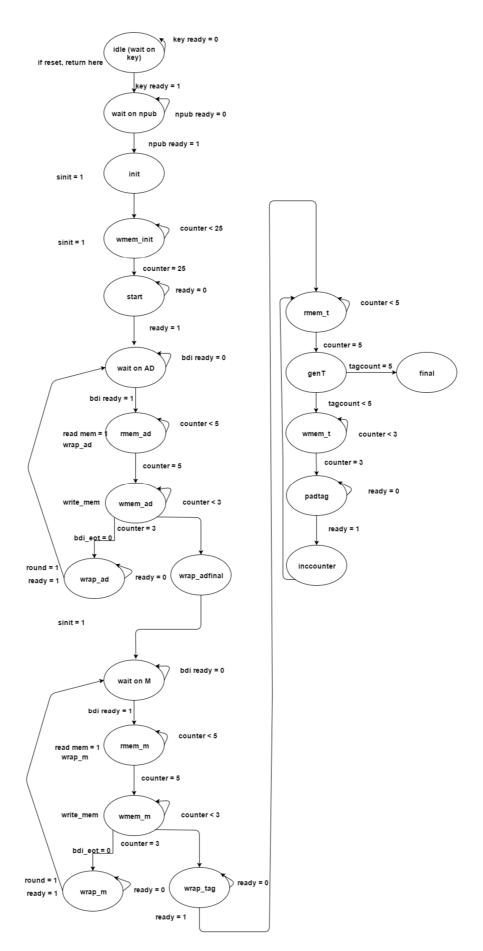

| Figure 4-12: Ketje area state machine                                          | . 45 |

| Figure 4-13: Ketje speed state machine                                         | . 47 |

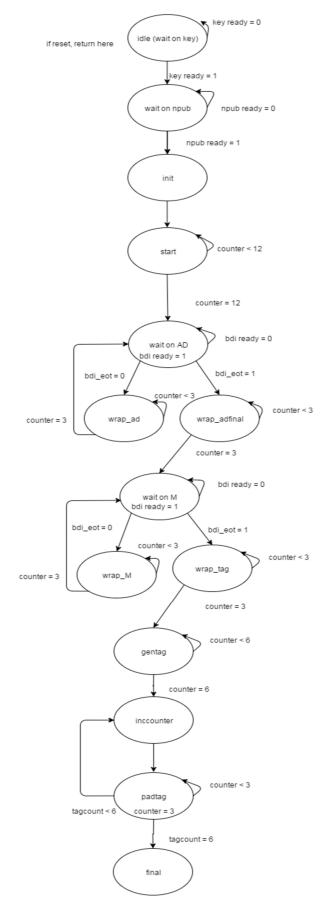

| Figure 4-14: Area optimised Ketje with less states                             | . 49 |

| Figure 4-15: Speed optimised Ketje with less states                            | . 50 |

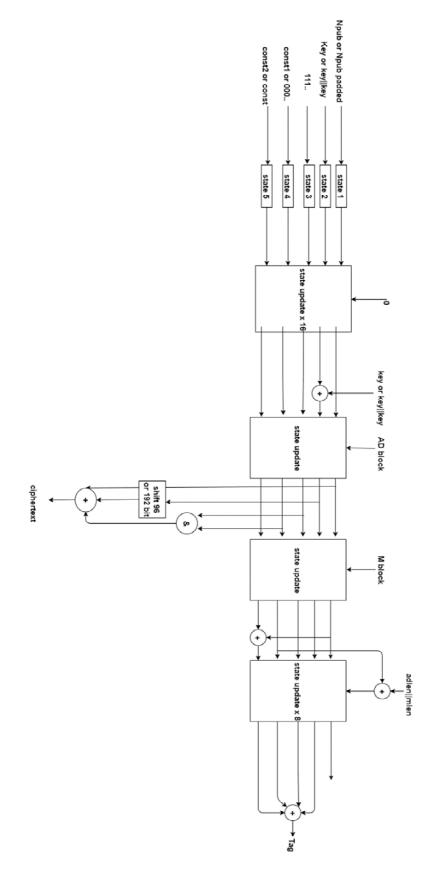

| Figure 5-1: The encryption process of MORUS                                    | . 56 |

| Figure 5-2: The state update function [26]                                     | . 58 |

| Figure 5-3: MORUS data path                                                    |      |

| Figure 5-4: MORUS state machine                                                | 61   |

# List of equations

| Equation 3-1: Vandermonde Matrix [17]                                                     |  |

|-------------------------------------------------------------------------------------------|--|

| Equation 3-2: Primitive polynomials of GF(2 <sup>32</sup> ) and GF(2 <sup>64</sup> ) [17] |  |

| Equation 3-3: Extended input generation [17]                                              |  |

| Equation 3-4: Throughput calculation [22]                                                 |  |

| Equation 3-5: Throughput calculation for short messages [22]                              |  |

| Equation 3-6 : Delay calculation in cycles                                                |  |

| Equation 3-7: Latency                                                                     |  |

| Equation 4-1: Input string to 3d matrix mapping [23]                                      |  |

| Equation 4-2: Round constant value [23]                                                   |  |

| Equation 4-3: rc constant value [23]                                                      |  |

|                                                                                           |  |

# List of graphs

| Graph 6-1: Throughput/ Area of CAESAR candidates (low Throughput)  | 7 |

|--------------------------------------------------------------------|---|

| Graph 6-2: Throughput/ Area of CAESAR candidates (high throughput) | 8 |

## List of abbreviations

| AD     | Associated data                                                                   |

|--------|-----------------------------------------------------------------------------------|

| AE     | Authenticated encryption                                                          |

| AEAD   | Authenticated encryption with authenticated data                                  |

| AES    | Advanced encryption standard                                                      |

| API    | Application programming interface                                                 |

| ASIC   | Application-specific integrated circuit                                           |

| ATHENa | Automated tool for hardware evaluation                                            |

| CAESAR | Competition for authenticated encryption: security, applicability, and robustness |

| COSIC  | Computer security and industrial cryptography                                     |

| DES    | Data encryption standard                                                          |

| DO     | Data output                                                                       |

| E&M    | Encrypt-and-MAC                                                                   |

| ECCode | Error correcting code                                                             |

| EOI    | End of input                                                                      |

| EOT    | End of type                                                                       |

| EtM    | Encrypt-then-MAC                                                                  |

| FF     | Flip-flop                                                                         |

| FM     | Field multiplier                                                                  |

| FPGA   | Field programmable gate array                                                     |

| FSM    | Finite state machine                                                              |

| GF     | Galois field                                                                      |

| HDL    | Hardware description language                                                     |

| I/O    | Input/output                                                                      |

| ISE    | Integrated synthesis environment                                                  |

| IV     | Initialization vector                                                             |

| LSB    | Least significant bit                                                             |

| LUT    | Lookup table                                                                      |

| MAC    | Message authentication code                                                       |

| MSB    | Most significant bit                                                              |

| MtE    | MAC-then-Encrypt                                                                  |

| Npub   | Public message number                                                             |

| Nsec   | Secret message number                                                             |

| PAR    | Place and route                                                                   |

| PDI    | Public data input                                                                 |

| RC     | Round constant                                                                    |

| SDI    | Secret data input                                                                 |

| SHA-3  | Secure hash algorithm 3                                                           |

| VHDL   | Very high speed integrated circuit hardware description language                  |

| WEP    | Wired equivalent privacy                                                          |

| XOR    | Exclusive or                                                                      |

### Abstract (Nederlands)

## Evaluation of CAESAR candidates on FPGA

Auteur: Jasper Gorissen Interne promotor: Prof. dr. ir. Nele MENTENS Externe promotor: Dr. Begül Bilgin Externe copromotoren: Dhr. Bohan Yang & Dhr. Danilo Šijačić

Het beveiligen van data is essentieel in ons leven. Omdat krakers manieren vinden om bestaande cryptografische algoritmen te kraken, moeten deze evolueren. Authenticated encryption (AE) biedt zowel confidentiality als authenticity van data simultaan aan. De nood voor AE is er gekomen nadat het combineren van bestaande algoritmen die confidentiality aanboden met die wat authenticity aanboden resulteerde in onveilige schema's. Nieuwe AE algoritmen worden ingezonden naar de CAESAR cryptografische wedstrijd. Onder andere, het departement Elektrotechniek (ESAT) van KU Leuven test deze algoritmen op sterkte en hardware prestaties om zo hun kwaliteit te bepalen.

Het doel van deze masterproef is het implementeren van drie CAESAR inzendingen: Trivia-ck, Ketje en MORUS in de AEAD API. Twee prestatie-eigenschappen die de mogelijke applicaties helpen bepalen, oppervlakte en snelheid, zijn gekozen als optimalisatiedoelwitten voor deze inzendingen. De implementaties zijn getest met ATHENa en Design Compiler.

De verschillende implementaties tonen de minimale oppervlakte en maximale snelheid van elk algoritme, alsook de afwegingen tussen de twee. De resultaten zijn ook vergeleken met andere CAESAR inzendingen, om zo een beter inzicht te krijgen in hun kwaliteit. Hier is aangetoond dat Ketje het kleinste oppervlakte heeft en dat MORUS een uitstekende snelheid/oppervlakte verhouding heeft. Trivia-ck, hoewel deze een hoge throughput heeft in de snelheid geoptimaliseerde versie, presteert niet goed in oppervlakte vergeleken met de rest.

### Abstract

## Evaluation of CAESAR candidates on FPGA

Author: Jasper Gorissen Internal supervisor: Prof. dr. ir. Nele MENTENS External supervisor: Dr. Begül Bilgin External co-supervisors: Dhr. Bohan Yang & Dhr. Danilo Šijačić

Data security is an essential part of our daily lives. However, cryptanalysts discover ways to crack existing cryptographic algorithms, making it necessary to improve them. Authenticated encryption (AE) offers the confidentiality and authenticity of data simultaneously. The need for AE has risen because combining existing algorithms that provide confidentiality with those that provide authenticity results in insecure schemes. New AE algorithms are submitted to the CAESAR cryptographic competition. Amongst others, the department of Electrical Engineering (ESAT) at KU Leuven tests the AE algorithms on their strength and performance to help determine their overall quality.

The goal of this thesis is the implementation of three CAESAR submissions: Trivia-ck, Ketje and MORUS, in VHDL, using the AEAD API. Two performance metrics, area and speed, which help determine the range of possible applications, are chosen as optimisation targets for these submissions. The implementations are tested on those metrics using ATHENa and Design Compiler.

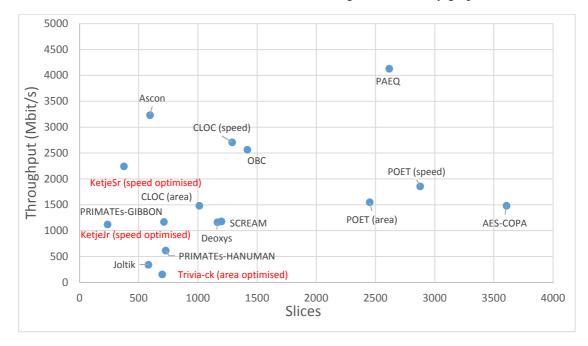

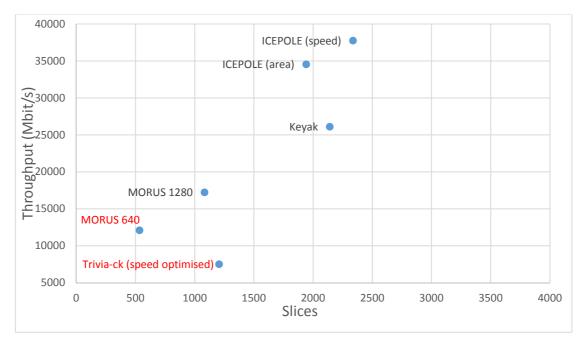

The different implementations show the minimal area and the maximal speed of each algorithm, as well as the trade-offs between the metrics. The results are also compared to other CAESAR submissions, in order to get a better perspective on the quality of the implementations. Here it shows that Ketje has the smallest area usage and MORUS has an excellent speed/area ratio. Trivia-ck, while having good throughput in the speed optimised version, underperforms in area usage compared to others.

## 1 Introduction

Cryptography is the field of research that encompasses the practice and study of techniques used to secure communication in the presence of unwanted third parties, which are called adversaries [1]. Cryptographic algorithms are used in many parts of our lives, from securing electronic payments and cell phones to internet security and many more. Algorithms used to encrypt and decrypt data are called ciphers. Encryption is the transformation of information from a useful form of understanding to an opaque form of understanding, and decryption is the opposite. This transformation of information is usually achieved by using a key. In symmetric key algorithms, data is encrypted using a secret key, and only those with the same secret key can decrypt the data. In the case of asymmetric key algorithms, two keys are used, one public and one secret, that are somehow paired together. The sender encrypts the data using the receiver public key, and now only the receiver can decrypt this data using his secret key.

The common goals in cryptography are message confidentiality, integrity and sender authentication [2]. Confidentiality is the privacy of the message, which is achieved by using a key as mentioned before. Message integrity (the ability to detect changes in the message content) and authenticity (being able to verify the identity of the sender) can be achieved by using a message authentication code (MAC). In order to achieve confidentiality and authentication at the same time, authenticated encryption algorithms are used. The need for this type of encryption has arisen from observations that combining secure encryption schemes (to provide confidentiality) with secure MACs (to provide authenticity) was difficult and prone to errors [3].

The other aspect of cryptology is cryptanalysis, which studies the methods on how to crack ciphers and their implementations. Since cryptanalysts discover new cryptanalytic attacks and have more powerful tools at their disposal to crack existing algorithms, cryptographic algorithms need to evolve. For instance, the data encryption standard (DES), the once predominant symmetric-key algorithm, was cracked by discovering the key in 22 hours and 15 minutes using brute force attacks, its weakness being its small 56-bit size [4]. In order to promote the creation of new algorithms, cryptographic competitions are organised. For instance, the advanced encryption standard (AES) competition was announced in 1997, called for "an unclassified, publicly disclosed encryption algorithm capable of protecting sensitive government information well into the next century" [5]. The winning algorithm, Rijndael, has superseded DES and is now used almost everywhere in secure applications, like bankcards and network security [5]. AES was followed by other competitions, like eSTREAM and SHA-3, each with their own focus. The latest of these competitions, CAESAR, focuses on authenticated encryption. CAESAR stands for 'Competition for Authenticated Encryption: Security, Applicability, and Robustness' [5].

In the competition, the submitted algorithms are tested against several cryptanalytic attacks to measure their strength as well on their performance, such as area usage, speed and power usage in hardware. These performance metrics help determine the range of possible applications. The smaller the hardware usage, the smaller the needed chip, the bigger the range of applications. The same goes for speed and power. An ideal algorithm will be secure, small and fast. The submissions are also tested on their performance in software.

The goal of this thesis is testing the area and speed hardware performance of several submitted CAESAR candidates. The chosen algorithms are Trivia-ck, Ketje and MORUS. They are tested on field-programmable gate array (FPGA) and application-specific integrated circuit (ASIC) chips. The difference between FPGA and ASIC is that FPGAs are premade chips, with a fixed number of logic

cells, depending on the chip, grouped together in slices, whereas in ASIC chips the number of logic gates is determined by the design. FPGA's are reprogrammable and are often used for prototyping. After the prototyping stage is done, developers usually switch over to ASIC, where they can control the area, timing etc.

The submitted algorithms are written in C-code or pseudocode, which can't be used to evaluate hardware. So this hardware code needs to be created, using a Hardware Description Language (HDL) such as VHDL or Verilog [6]. The objective of this thesis is to investigate the minimal area usage and maximal speed of each algorithm, and investigating the trade-offs between these two metrics. In order to achieve this, two versions of the code are created, one that is optimised for speed and another for area. Two different implementations are needed because most optimisations used to improve one characteristic will be at cost of the other. This code then needs to be embedded in an application programming interface (API), which allows the outside world to interact with the algorithm. The results on area and speed are then used in a comparative study to determine the quality of the algorithms regarding these metrics.

This thesis is done in cooperation with ESAT. ESAT is the department of Electrical Engineering of KU Leuven that does research on international level and offers academic level education on the subjects of electronics, electrical engineering and information processing. The department also explores a wide array of technological innovations in the field of energy, integrated circuits, image and voice processing and telecommunication systems [7].

COSIC, which stands for Computer Security and Industrial Cryptography, is a research group branched of ESAT that specializes in digital security. Their studies are applied in a broad range of domains, like electronic payments, communication, electronic ID, e-voting and the security of edocuments. Their research focus lies in the development of security architectures for information and communication systems, the building of security mechanisms for embedded systems and the design, evaluation and implementation of cryptographic algorithms and protocols [8].

In Section 2, the motivation for the chosen algorithms is given. The used programs are also discussed briefly. Sections 3, 4 and 5 offers a more in-depth look at the algorithms and their respective VHDL code and optimisations. In Section 6, the results are compared with one another and with other implementations and in Section 7, the conclusions are presented.

## 2 Materials and methods

#### 2.1 Authenticated encryption

The concept of authenticity first appeared in the banking industry. Banks did not want to transmit their data and allow an attacker to flip bits undetected. Here the attacker would not need to decrypt the message, however flipping bits would make the encrypted message say "Post \$800" instead of "Post \$100" for instance [3]. At first, primitives that offer confidentiality and authenticity had been designed separately. Combining these two resulted in weak systems, such as the wired equivalent privacy (WEP), which used a cyclic redundancy check as hash function alongside a stream cipher for encryption. WEP keys could be cracked in minutes using simple hardware and computers [9]. So there was a need to find a way to combine a strong authentication mechanism with a strong cipher. Hugo Krawczyk published a paper in which he examined three commonly used combination methods [10]. These methods are EtM (encrypt then MAC), MtE (MAC then encrypt) and E&M (encrypt and MAC).

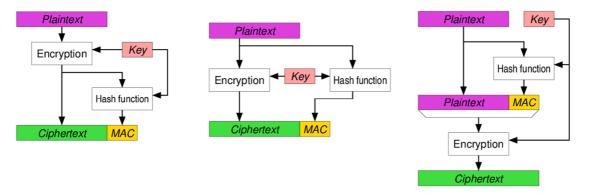

Figure 2-1: left: EtM, middle : E&M, right: MtE [11]

For their encryption input, these schemes use a key, message and optionally a header that will not be encrypted and instead is covered by authenticity protection. The output for encryption is the ciphertext and the tag or MAC. During decryption, the inputs are the ciphertext, tag and the optional header, which will then output the original message if the outputted tag is equal to the transmitted one.

In the beginning of the thesis, the choice was offered between the 30 CAESAR submissions that made it to the second round. The candidates that were chosen can be found in Table 2-1.

| Cipher    | Based on (type)            | IV (bits) | Key (bits) | State (bits) |

|-----------|----------------------------|-----------|------------|--------------|

| Trivia-ck | Trivium (Stream cipher)    | 128       | 128        | 385          |

| Ketje     | KECCAK-f (Sponge function) | 80/128    | 96/128     | 200/400      |

| MORUS     | LRX (Stream cipher)        | 128       | 128/256    | 640/1280     |

Table 2-1: CAESAR candidates

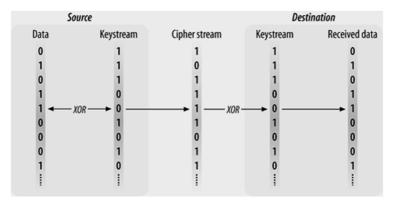

Trivia-ck has been chosen because of previous experience with Trivium on which the cipher is based. Trivium is a stream cipher. This type of cipher combines its plaintext with a pseudorandom digit stream, one digit at a time. Stream ciphers usually have a smaller hardware footprint and are faster than block ciphers [12].

Figure 2-2: Generic stream cipher [13]

MORUS, the other AE algorithm based on a stream cipher, was chosen for its resemblance to Triviack. Using this is interesting to see the differences in performance when comparing the two. It is also an algorithm built for speed, with 128/256 bits output per cycle and a fast state update function.

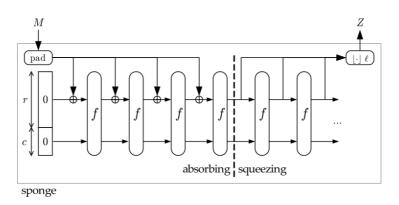

Ketje has been chosen since it shares the same permutation with KECCAK, of which a subset was chosen to be the new SHA-3 standard in 2007. Ketje is a sponge construction, which takes an input bit stream of any length to produce an output with a desired length in two distinct phases: absorbing, where the input is read into the state, and squeezing, where the state returns the output blocks. A more detailed explanation of the sponge construction is given in Section 4.

Figure 2-3: The sponge construction [14]

#### 2.2 Used programs

During the course of the thesis, a number of programs are used for various purposes. These are: Xilinx integrated synthesis environment (ISE) WebPACK design software, the hardware Application Programming Interface (API) AEAD, ATHENa and Design Compiler. This section outlines them briefly.

#### 2.2.1 Xilinx ISE WebPACK

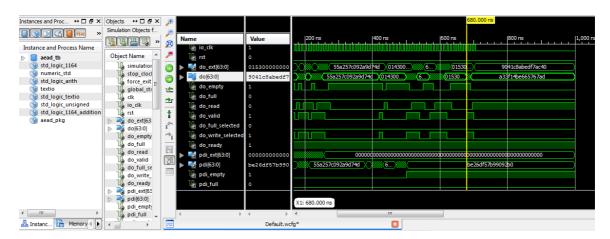

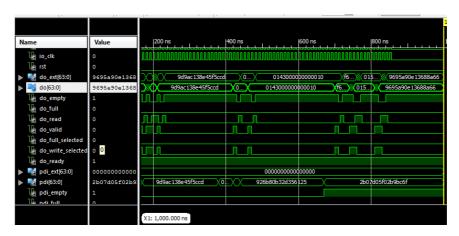

The Xilinx ISE is a software tool used for the synthesis and analysis of hardware description languages (HDL) designed by Xilinx. It can be used to generate timing reports and area consumption on several Xilinx FPGA families, like the Spartan and Virtex FPGA's. Since the WebPACK is a free licence, not all of the mentioned families are available. It is mainly used in this thesis for its ISim simulator. Using ISim, the HDL code can be tested by simulating input signals and observing and verifying the output of the device under test.

Figure 2-4: An ISim testbench output

As mentioned, the code is written in HDL, which is a specialized language to program digital logic circuits. There are two major HDLs: VHDL and Verilog. The one used in this thesis is VHDL because past experience with the language, but since the two languages are very similar, the code can be converted from one to another easily.

#### 2.2.2 AEAD API

AEAD is a proposed universal hardware API for authenticated ciphers. In the call for CAESAR candidates, the software API has been clearly defined. The result is that software implementations can be compared equally. However, no similar hardware API has been proposed. As a result, hardware implementations use independently made API's, which can have a high influence on area and throughput, resulting in unreliable comparisons between the candidates [15]. The AEAD API offers several features like allowing input of an arbitrary size (a multiple of bytes only), a wide range of data port widths (between eight and 256), independent data and key inputs, support for encryption and decryption within the same core and more. The AEAD interface has three major data busses: one for public data (the associated data, the message, the public message number and tag), one for secret data (the key) and one for data outputs (the ciphertext and tag). Each of these busses have their own handshaking signals *valid*, which indicates that data is ready at the source, and *ready* which indicates that the destination is ready to receive. The interface is shown in Figure 2-5.

Figure 2-5: AEAD interface [15]

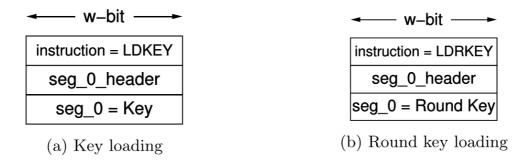

The format of the secret data input (SDI) starts with an instruction, which is either Load Key or Load Round Key, followed by the key or round key segments, whose size is determined by the width of the SDI. Each segment will have their own header.

Figure 2-6: Two formats for SDI [15]

The format for the public data input (PDI) is similar. It starts with an instruction: activate key (ACTKEY), authenticated encryption (ENC) or authenticated decryption (DEC). The activate key instruction, which is used to couple the secret key with this input, is called first, then either authenticated encryption or decryption. During encryption, the public data is segmented in the public message number (Npub), secret message number (Nsec), associated data (AD) and the message. During decryption, the segments are the same but include the ciphertext instead of the message, the encrypted secret message number instead of the Nsec, and the tag.

Figure 2-7: Formats for PDI. (a) is encryption, (b),(c) and (d) show decryption and the resulting pass or fail [15]

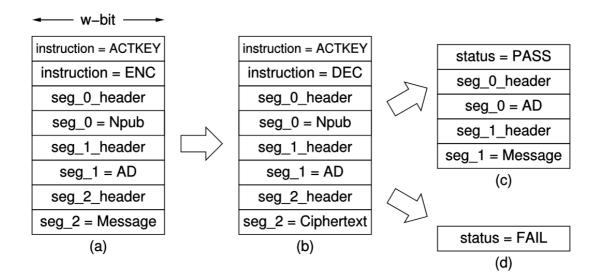

Each segment will have its own header that determines its type and length. It also notifies if it's the last of its type, or the last of the input.

Figure 2-8: The segment header [15]

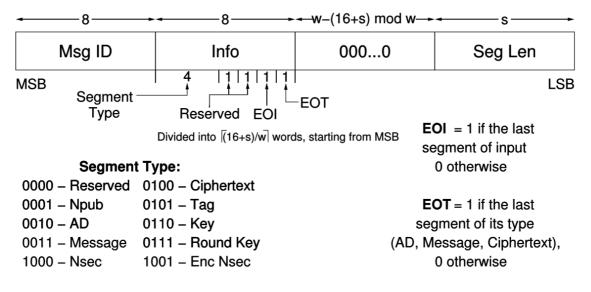

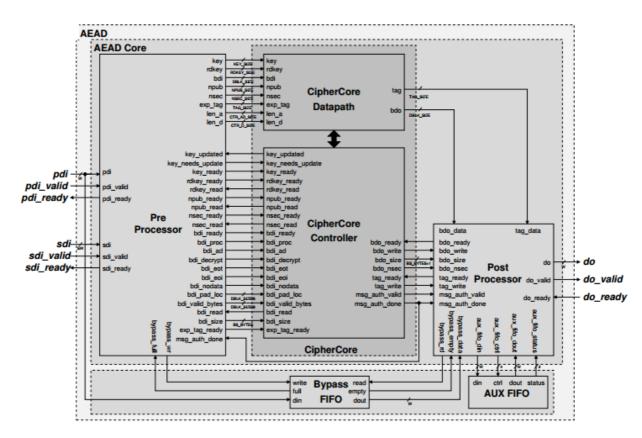

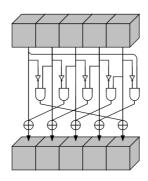

The AEAD interface is built up out of three parts: the pre-processor, the post-processor and the ciphercore. The pre-processor parses the segment headers, loads the keys and input blocks, pads the input blocks and keeps track of the number of data bytes left to process. The post-processor clears the padding out of the ciphertext or plaintext, converts the output blocks back into words and formats them into segments. During decryption, it stores the messages until the result of authentication is known. The ciphercore is the actual cipher algorithm.

Figure 2-9: The AEAD interface [15]

In order to work with the AEAD interface, the ciphercore state machine is required to have the following state groups: *load/activate key*, *process AD*, *process message or ciphertext* and *generate or verify the authentication tag*. During the first state group, *load/activate key*, the state machine monitors the *key\_needs\_update* and *key\_ready* inputs. *Key\_ready* is high when the key is successfully loaded into the pre-processor. When the *Activate Key* instruction is received, the *key\_needs\_update* goes high. When both of these inputs are high, the ciphercore can read the key and set the *key\_updated* output to high. This output remains high until a new key is needed.

After the key is read, the npub is next, using the *npub\_ready* input to monitor its status and the *npub\_read* output to move on to the processing the AD. Now the ciphercore needs to monitor the *bdi\_ready*, *bdi\_eot* and *bdi\_eoi* inputs. For each block of AD read, the *bdi\_read* output is set to high, and it waits for the next block until *bdi\_ready* is high. This sequence repeats until the whole AD is read and the *bdi\_eot* goes high. Then the message is read and monitored using the same inputs. During this group of states, the ciphertext is written to the post-processor using the *bdo\_write* output. In the final group of states, the tag is generated and written to the post-processor using the *write\_tag* command.

#### 2.2.3 ATHENa & Design Compiler

ATHENa, the Automated Tool for Hardware EvaluatioN is aimed at a fair, comprehensive and fully automated evaluation of hardware cryptographic cores [16]. Results of comparison depend on the algorithms, but also on the selected hardware architectures, implementation techniques, the family of FPGA and used tools. ATHENa is an open-source tool that allows for an automated generation of optimized results for multiple hardware platforms. It is used alongside the AEAD hardware API in order to produce generalized, fair results. Each time ATHENa runs, it generates results for Xilinx and Virtex chip families. The results given are the area in slices and look up tables (LUT) and the timing in synthesis frequency and post place-and-route frequency. If selected, it can also present the best fitting device for said implementation.

Design Compiler by Synopsys is a logic-synthesis tool that is used in the design of an ASIC chip. It can be used to get the hardware area in  $\mu$ m, or in the amount of logic gates and timing in clock period. For this thesis, the free NangateOpenCell PDK 45nm library is used as the target and link library.

In this thesis, ATHENa is used to generate the FPGA results, whereas ASIC results are generated using Design Compiler. In Section 6, the Trivia-ck, Ketje and MORUS results are compared with other authenticated encryption algorithms from the ATHENa database.

#### 3 Trivia-ck

#### 3.1 Algorithm

Trivia-ck is an AE algorithm based on a stream cipher that uses a 128-bit key and a 128-bit nonce [17]. The nonce is divided into two 64-bit parts: param, which is a bitwise representation of the ck version, and the npub. The algorithm uses an internal state of 385 bits and outputs a 128-bit tag. Trivia-ck is described by the integrated combinations of the Trivia-SC and VPVHash modules. Trivia-SC is the stream cipher used to encrypt the message and VPVHash is used to generate the tag. The ck in the algorithm is used for the length of the intermediary tags, which get outputted after every 64-bit message block. The designers recommend two versions: Trivia-0 and Trivia-128. The first does not output the intermediary tags, while the latter outputs 128-bit intermediary tags [17]. A circuit diagram of Trivia-ck can be observed in Figure 3-1 below.

Figure 3-1: Trivia-ck circuit [17]

In the first step, both the key and nonce are loaded into the state. The state is divided into three nonlinear feedback registers A, which is 132-bit, B, which is 105-bit and C, 147-bit. The key is padded with "1" and loaded into register A., while a padded IV gets loaded into C. B is initialised with "1".

After this, the state is updated for 1152 rounds. However, this updating can be parallelized up to 64 bits thanks to the flexibility of the Trivia-SC module, allowing the amount of rounds to be reduced to

18. Once the initialisation is done, the first 64 bits of the associated data is loaded into VPVHash alongside the first 64-bits of the stream (the StExt64 module in Figure 3-1). This step gets repeated until the whole associated data (AD) has been introduced. If the AD is not divisible by 64, the last block will be padded using 10\* padding. If there is no AD, there will be a single 10<sup>63</sup> "empty" block. After the AD step is done, the intermediary tag is generated in four extra clock cycles, by using the first and third state key and xoring this with the VPVHash output tag. This 160-bit intermediary tag is inserted into the state by xoring it with register A and the first 28 bits of B.

Before processing the message, the stream is updated again for 1152 rounds. When this is done, the message gets introduced in the same way as the AD (in 64-bit slices). The difference with the AD step is that with each 64-bit message block, a 64-bit ciphertext is outputted by xoring the message with the state key. After the message is fully introduced and the ciphertext is generated, the 128-bit tag is generated in three extra clock cycles. If ck is zero, then no extra tags are generated, when it is 128, the VPVHash tag is outputted every step [17].

The decryption works in a similar way, where the inputs are AD, nonce, Key, ciphertext and tag. By running the code with the ciphertext as the message, the outputted ciphertext will be the original message if the outputted tag is equal to the transmitted one.

It is important to note that this describes the first version of Trivia-ck. For the second CAESAR round, Trivia-ck has been updated to version two. In this version, the biggest change is that a 128-bit intermediary tag is generated instead of a 160-bit one, which allows the algorithm to use only one VPVHash block for both the intermediary tag and the final tag(s), saving more hardware space [18]. However the developer C-code for the second round have not been updated. A prototype has been designed for the second version in order to measure the differences against the first version, but these results are not necessary correct, since there is no way to verify the testbench results yet.

In Section 3.1.1 and 3.1.2, the Trivia-SC and VPVHash modules are examined more closely.

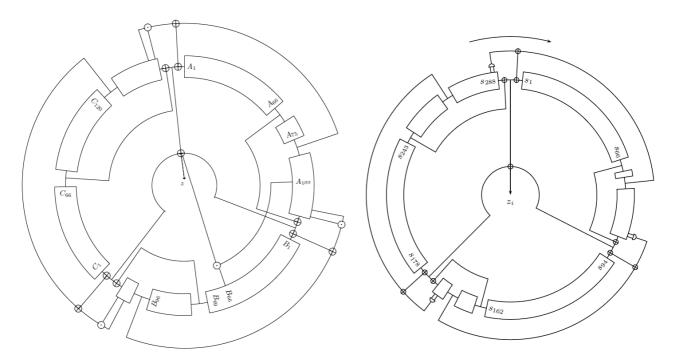

#### 3.1.1 Trivia -SC

Trivia-SC is a variant of Trivium. This is a hardware oriented synchronous stream cipher that was designed for simplicity, without sacrificing security, speed or flexibility. It uses a 80-bit key and nonce and a 288-bit internal state and provides 80-bit security [19]. It is flexible in that the amount of iterations done in one clock cycle can be altered to suit the design. This is achieved by ensuring that any state bit is not used for at least 64 iterations after it has been modified. So it allows for up to 64 iterations to be calculated in parallel by duplicating the AND and XOR gates. This flexibility makes it easy to optimise for speed or area.

| Components | 1-bit | 8-bit | 16-bit | 32-bit | 64-bit |

|------------|-------|-------|--------|--------|--------|

| Flip-flops | 288   | 288   | 288    | 288    | 288    |

| AND gates  | 3     | 24    | 48     | 96     | 192    |

| XOR gates  | 11    | 88    | 176    | 352    | 704    |

| NAND gates | 3488  | 3712  | 3968   | 4480   | 5504   |

Table 3-1: Estimated gate counts of 1-bit to 64-bit hardware implementations [19].

Trivia-SC extends Trivium by adding several extra modules, increasing the Key, IV and internal state size and introducing a non-linear effect in the key computation [17]. It extends the Trivium modules *Load*, *Update* and *KeyExt* by *StExt64* and *Insert*. *Load* inserts the 128-bit Key and IV into the internal state, *Update* updates the stream, KeyExt extracts the keystream from the state, *StExt64* extracts the first 64-bits from the state and finally *Insert* inserts an intermediary tag into the stream. The pseudocode of these modules can be found in the appendix. Just like Trivium, Trivia-SC is parallelizable up to 64 bits.

Figure 3-2: The Trivia-SC cipherstream (left) and the Trivium cipherstream (right) [17], [19]

#### 3.1.2 VPV-Hash

The second component, VPV-Hash is used to compute the tag in three steps. The first step is calculating the checksum by applying Vandermonde based error-correcting code, called ECCode. Then it calculates the Pseudo-dot product of the checksum and the Trivia-SC state and finally, it calculates the Tag by using ECCode again [17].

ECCode is an error correcting code that extends its input by a distance d. The extra output is calculated via the Vandermonde Matrix and Horner's rule. The Vandermonde matrix is shown in Equation 3-1.

$$V_{n,d,l} \begin{bmatrix} 1 & \dots & 1 & 1 & 1 \\ \alpha^{l-1} & \dots & \alpha^2 & \alpha & 1 \\ \dots & \dots & \dots & \dots & \dots \\ \alpha^{(l-1)(d-1)} & \dots & \alpha^{2(d-1)} \alpha^{d-1} & 1 \end{bmatrix}$$

Equation 3-1: Vandermonde Matrix [17]

In this construction, the primitive polynomials used to represent the Galois fields  $GF(2^{32})$  and  $GF(2^{64})$  respectively can be found in Equation 3-2. The  $\alpha$  used in Equation 3-1 is the primitive element of those Galois fields and is noted as  $\alpha_{64}$  or  $\alpha_{32}$ .

$$p_{32}(x) = x^{32} + x^{22} + x^2 + x + 1$$

$p_{64}(x) = x^{64} + x^4 + x^3 + x + 1$

Equation 3-2: Primitive polynomials of GF(2<sup>32</sup>) and GF(2<sup>64</sup>) [17]

The primitive element multiplication can be easily achieved using shift and bit-wise xor operations. The extended output  $y_1$  to  $y_d$  is calculated through matrix multiplication of the Vandermonde Matrix with the original input, as shown in Equation 2 below.

$$\begin{pmatrix} y_1^k \\ y_2^k \\ \vdots \\ y_d^k \end{pmatrix} = \begin{pmatrix} 1 & \dots & 1 & 1 & 1 \\ \alpha^{k-1} & \dots & \alpha^2 & \alpha & 1 \\ \alpha^{2(k-1)} & \dots & \alpha^4 & \alpha^2 & 1 \\ \vdots \\ \alpha^{(d-1)(k-1)} & \dots & \alpha^{2(d-1)} & \alpha^{(d-1)} & 1 \end{pmatrix} \cdot \begin{pmatrix} x_1 \\ x_2 \\ \vdots \\ x_k \end{pmatrix}$$

Equation 3-3: Extended input generation [17]

In the first step of VPV hash, this extended output is the checksum and in the last step it is the tag. The pseudo-dot product is a multiplication of two 32-bit signals, one being the extracted key of the Trivia-SC block and the other the output of the first ECCode (which is either the associated data or the message extended with the checksum).

#### 3.2 VHDL code

In this section, the design of the VHDL code is outlined in a "top-bottom" way. First the top level block is illustrated. Then the two subcomponents, the data path and the state machine are examined, as well as their underlying components.

#### 3.2.1 Top level block

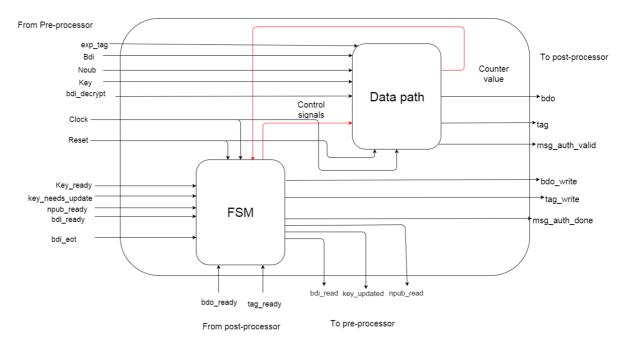

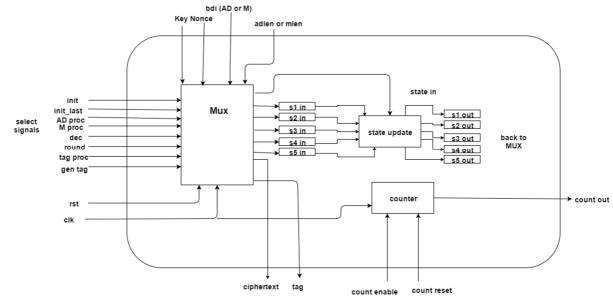

The code is divided into two parts, one part that takes care of the calculations, called the data path and another that controls the program flow, called the FSM. This is done to ease bug fixing and making adjustments, while also granting a better overview of the code. The top level block combines the inputs and outputs of these blocks together as shown in Figure 3-3. Since this top level block is similar for Ketje and MORUS, it will only be shown here.

Figure 3-3: Trivia-ck ciphercore

#### 3.2.2 Data Path

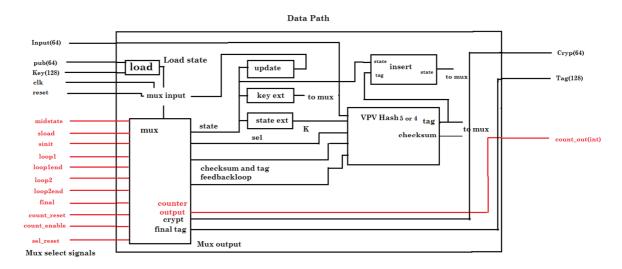

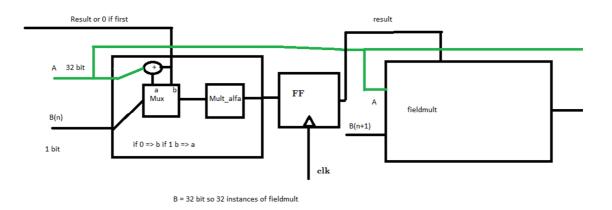

The data path contains all the functional units, such as logic gates and multipliers. It contains several smaller blocks, which represent the two mathematical components Trivia-SC and VPVHash. The data path is illustrated below in Figure 3-4.

Figure 3-4: Trivia-ck data path

The load, update, key\_ext, insert and st\_ext blocks are all made up of simple registers, flip flops and logic gates. The multiplexer shown here is controlled by the state machine and routes the right signals to the right blocks and outputs. The *sload* signal routes the load block output to the state registers. *Sinit* and the *loop* inputs route the state registers to the update, key ext and state ext blocks. The *loop* inputs additionally routes the checksum and tag to the VpVhash block, while *loopend* routes the tag only.

The *midstate* inserts the tag into the state and *final* outputs the tag. During *loop2*, the ciphertext is also outputted. A counter is also used to count the rounds needed per state.

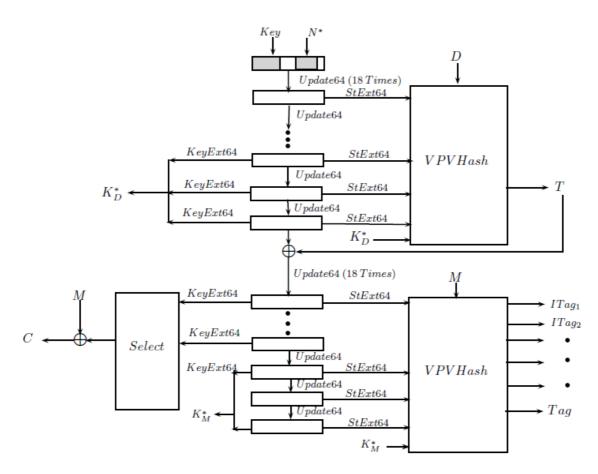

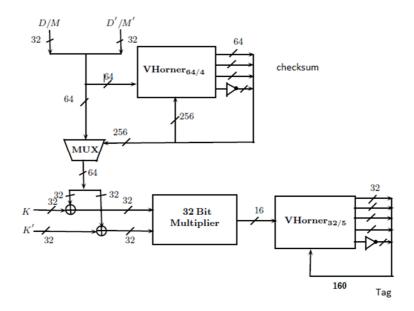

There are two version of the VPVHash block, one outputting a 160-bit tag and one outputting a 128bit tag. They both contain several smaller components, shown in Figure 3-5.

Figure 3-5: VPVhash [17]

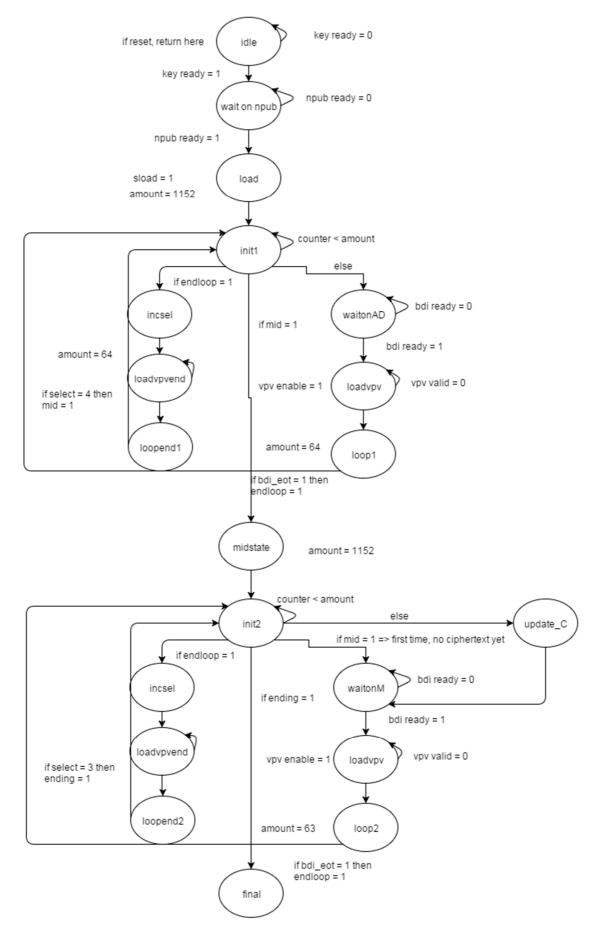

As can be seen in Figure 3-5, VPVHash is built up out of two Vhorner blocks, a multiplexer and the 32-bit field multiplier. VHorner64 has two inputs: the 64-bit message or AD, and the 192-bit or 256-bit checksum, depending on the VPVHash block. The input checksum gets multiplied by the primitive element  $\alpha_{64}$ , which is achieved by using a shift register. This new checksum then gets xored by the input to produce the output checksum. The output checksum then used as the new input checksum next clock cycle. The multiplexer first sends the message or AD in 64-bit chunks to the multiplier. After the last block, its 256-bit checksum is sent in 64-bit chunks. The 32-bit multiplier has two inputs, the 64-bit message or checksum from Vhorner64 gets xored with the 64 first bits of the cipher stream.

This result then gets split into two 32-bit parts to form the inputs. The multiplier is shown in Figure 3-6.

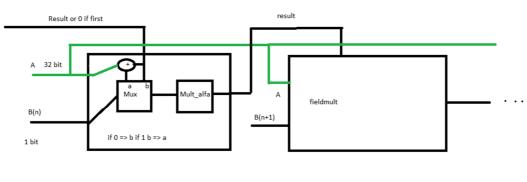

B = 32 bit so 32 instances of fieldmult

The field multiplier includes a multiplexer and a primitive element shift register. As illustrated in Figure 3-6 above, there are 32 instances of this block, one for each bit in input B. If this bit is zero, the input result (which is zero for the first block and the output of the previous block for the other blocks) gets multiplied with  $\alpha_{64}$ , otherwise the input is first xored with A and then multiplied with the primitive. This multiplication is done by shifting and xoring the bits in a specific way. The result is the output of the FM block. The final FM block is different from the other FM blocks in that there is no multiplication with  $\alpha$ . The multiplier output is then used in Vhorner32, which works identical to Vhorner64 except it multiplies its input tag with  $\alpha_{32}$  and outputs a 160-bit or 128-bit tag.

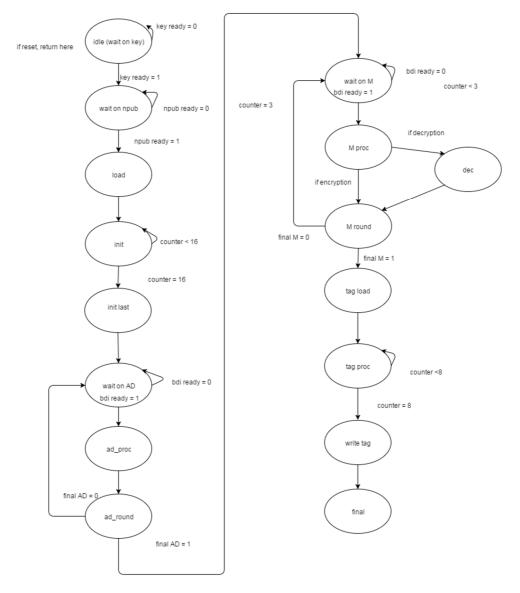

## 3.2.3 Finite State Machine

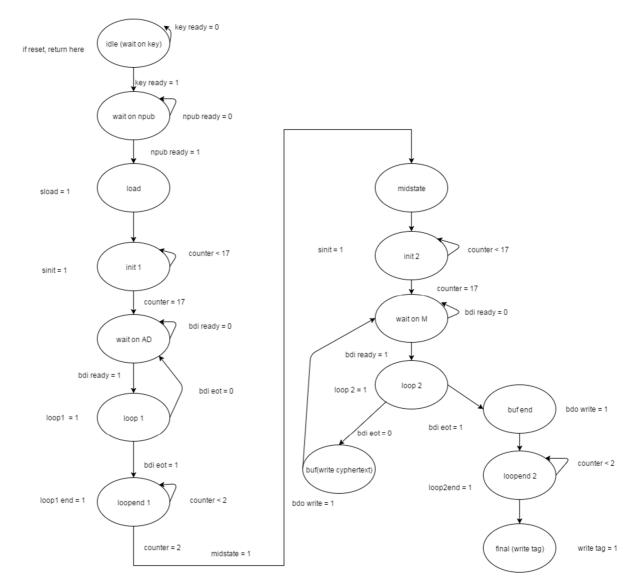

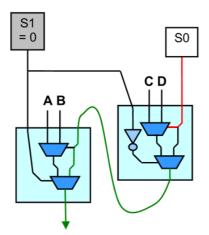

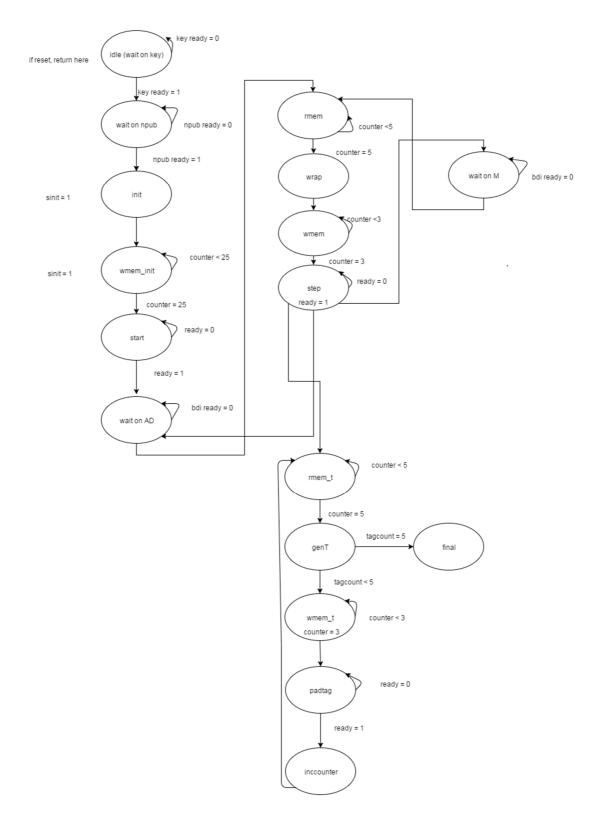

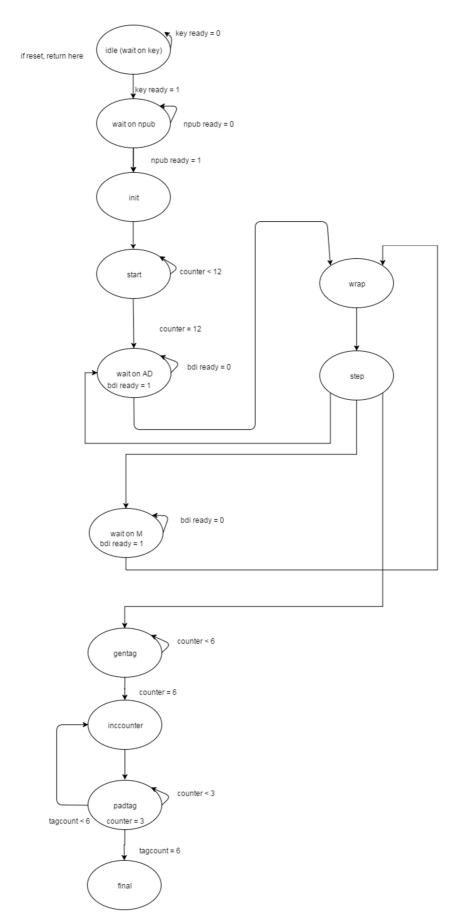

The state machine controls the large multiplexer in the data path, which in turn controls the internal signals. This state machine has 20 states, in which 16 states are used to cipher or decipher the message and four states which are needed to interact with the AEAD structure. The first two states wait for the AEAD wrapper to read the key and npub. After this, in the *load* state, the IV and key are loaded into the stream. The following state, *init*, initialises the stream. After this, during the *loop1* state, the AD is loaded in 64-bit chunks into the VPVhash. Each *loop1* state calculates the tag and checksum and routes it back into the Vhorner blocks next clock cycle. After all the AD are read, *loop1end* state is called. In this state the 160-bit tag is calculated. This takes four clock pulses because the mux output is 64 bits and the checksum is 256 bits. Also the streamkey of the first and last step are taken here, which are xored with the tag to calculate the intermediary tag. In the *midstate*, this intermediary tag is inserted into the stream. Then the process repeats itself for the message, where in every buffer state the 64-bit chunk of the ciphertext is written to the post-processor. In the *final* state, the tag is written to the post processor and the state waits for a new key. The state machine is illustrated in Figure 3-7.

Figure 3-6: Field multiplier

Figure 3-7: Trivia state machine

## 3.3 Trivia-ck optimisation

In order to test the algorithm fairly in both speed and hardware usage, the code has been improved using these two optimisation strategies. The first goal is to discover the areas which could use improvement. Here, both the multiplier in VPVhash and the parallelizable Trivia-SC module are obvious candidates. In the original code, 32 instances of the multiplier are used, resulting in a large amount of registers. It is also a critical path for the clock, since all calculations happen serial, decreasing the maximum frequency. Also, in the original code, the update and key exit block update 64 bits per clock cycle. This also requires a large number of registers. In the following paragraphs the original code, the area and speed optimisations are discussed. As mentioned before, the basic code and most optimisations were done on the first, outdated version of Trivia-ck. A prototype for the new version of the code is discussed in Section 3.3.4. The results for area usage and timing can be found in Section 3.3.5.

### 3.3.1 Basic code

In order to observe the impact of the optimisations on the algorithm, the basic version is discussed first. In this version, no optimisation path is followed and the blocks use their recommended parameters. This version uses 64-bit parallel update and key generation, 32 instances of the multiplier without pipelining and two VPVhash. It also uses a normal binary counter and 5:1 multiplexers in the VPVhash block. Shown below are the testbench results of the ciphercore for a 15 byte AD and a 16 byte message, resulting in three 64-bit ciphertext chunks. The results for this version are found in Section 3.3.5.

Figure 3-8: Testbench results from the basic Trivia-ck version

## 3.3.2 Area optimisations

This section outlines all the area reducing optimisations. The performed optimisations are: rolling up on the 32-bit multiplier, reducing 64-bit update to 1-bit and changing the multiplexer. The Vhorner block was also rolled up, but this resulted in more area, so this change was ultimately undone.

The first optimisation is rolling up the 32-bit multiplier. The original field multiplier block is built up out of 31 identical FM blocks and one final FM block. All of these blocks are connected using 32 32-bit signals.

The rolled up version of the field multiplier only uses one FM block and the FM last block, which are connected using only three 32-bit signals. The FM blocks in the original code differ only in the bit of B they monitor. By using a counter, the 32 bits of B are sent to the FM block bit by bit. The *result\_out* output is routed back to the input every clock cycle. After 31 cycles, the FM last block output is the final result. For every time the multiplication result is needed, the code needs 32 clock cycles to process it, which is during every *loop* (processing AD and message) and *loopend* (tag generation) state. This results in higher delay and latency, which can be calculated using Equation 3-5:

$$encryption \ delay \ (cycles) = 262 + \frac{Mlen}{64} \cdot (1+32) + \frac{ADlen}{64} \cdot (1+32)$$

In order to further reduce the registers, VHorner was also rolled up. In the basic code, each VHorner uses four internal registers of 128-bit, 160-bit 192-bit or 256-bit. From each of these registers, 32 or 64 bits are taken to form the tag or checksum, after being multiplied by  $\alpha$ . In order to reduce the code to use only one register, VHorner was rolled up, so that the multiplication and checksum or tag would be generated in four cycles. However, the added control scheme needed for this increased the total area, so this optimisation was not used.

The second optimisation is reducing the amount of XOR- and AND-gates used in the update and key\_ext blocks. This is achieved by only updating one bit at a time instead of 64-bits parallel, which is possible since Trivia-SC ensures that any state bit is not used for at least 64 iterations after it has been modified. Now 64 clock cycles are needed every time the state is updated. This means 2304 clock cycles are needed for the two initialisation states, and 64 extra for every message and AD block and 448 extra for the tag generation.

The last area focussed optimisation is changing the multiplexers used in the VPVHash blocks. In the original code, the two VPVHash blocks use a 5:1 multiplexer with a 3-bit select signal. During synthesis, such a multiplexer is built up out of four 2:1 multiplexers (N-1 2:1 mux, where N is the amount of inputs). Here, each 2:1 mux requires a separate LUT, which results in four LUTs [20]. It is however more efficient to use one 4:1 mux and one 2:1 mux to create the 5:1 mux. The 4:1 mux used two LUTs, which results in three LUTs total. A 4:1 is built as depicted in Figure 3-9 below.

Figure 3-9: A 4:1 mux using 2 LUT's [20]

In the VPVHash4 block, the multiplexer only has four inputs, which allowed a single 4:1 mux after changing the code. This change resulted in better area but also better timing, so these mux trees are also used in the speed optimised version.

A lot of the optimisation increased the total amount of clock cycles needed for encryption and decryption, which results in more states in the state machine. The new state machine is shown in Figure 3-10.

The loading of the key and npub remains the same. The initialisation state is used to update the stream. After loading the key and npub, the stream now gets updated 1152 times, since it now happens bit by bit.

After this, the FSM waits on the AD blocks. After each block, the 32-bit multiplication is calculated over 32 clock cycles during the *loadvpv* state. After this, the Pre-processor is notified that the block is 20

read and the stream is updated 64 times in the init state. When all the AD blocks are read, the init state continues to the *incsel* state. This state increments the select signal for the multiplexers in the VPVHash blocks. Thereafter, the multiplication is calculated in the *loadvpvend* state and the tag is calculated in the *loopend2* state. Then, the state is updated again for 64 times. This gets repeated four times to calculate the valid tag. The processing of the message blocks is similar. The *update\_C* state generates the ciphertext and is called after updating the stream, after the message block has been read.

Figure 3-10: state machine for the area optimisation

## 3.3.3 Speed optimisations

This section outlines all the speed optimisations. The performed optimisations are: pipelining the field multiplier, changing the VPVHash multiplexers and selecting a better counter. Also, several registers where duplicated in order to shorten the path delays.

The first optimisation is reducing the critical path by pipelining the field multiplier. This path starts in the data path control multiplexer input. Whenever *loop1, loop2, loop1end* or *loop2end* are high, the tag gets generated in the VPVhash block. Here, the field multiplication takes place. In the basic version, 32 of these FM blocks are utilised every clock pulse. Since each of these blocks uses a 32-bit 2:1 multiplexer, using them all at once slows the code down considerably. However, this critical path can be broken up using intermediary registers. This technique is called pipelining. Although a pipelined circuit requires more clock cycles to complete, the maximum clock frequency increases, which results in higher throughput. The benefits of pipelining can be explained using a simple example: if 5 bits of data have to be transferred over a path with a 2 ns delay, bit for bit it will take 10 ns to complete. When this path is pipelined, the path delay is lowered, for instance to 1 ns. It will however take one extra clock cycle to get the final bit, thus 6 cycles are needed. So the data only takes 6 ns as opposed to the 10 ns it took in the non-pipelined path. In this optimisation, 31 extra registers are implemented, one between every FM block.

Figure 3-11: Pipelined field multiplier

It takes 32 clock pulses to get the multiplier output to the VHorner4 block to generate the tag. However, since the tag is only needed during the *midstate* and the *final* state, the total added delay is only 64 clock pulses, independent of the AD and message length.

Another change is switching from the 5:1 multiplexer to the 4:1 and 2:1 multiplexer, as explained in the area optimisations. This optimisation also results in faster clock frequencies.

The counter used in the state machine is also changed from binary to one-hot. In the basic code, this timer is written as shown below.

counter: process(clk,count\_reset,count\_enable)

begin

And this is how the counter is read:

If (count\_in < 3) then

Here, the code needs to check several bits in order to compare the count in value with the number. This takes extra time [21]. The process can be increased in speed if the code only needs to compare a single bit instead like so:

if  $(count\_in(3) = '1')$  then

In order to achieve this, the counter is changed form a normal incrementing counter to a shift register, where a '1' is loaded as the LSB (last significant bit) and this '1' gets shifted to the left every clock pulse, like demonstrated below.

```

counter: process(clk,count_reset,count_enable)

```

begin

if (count\_reset = '1') then

count\_out\_buffer(35 downto 1) <=(others =>'0');

*count\_out\_buffer(0) <= '1';*

elsif(rising\_edge(clk)) then

$if(count\_enable = '1')$  then

count\_out\_buffer <= count\_out\_buffer(34 downto 0) & '0';</pre>

end if;

end if;

end process;

In order to give the pipelined field multiplier time to compute the product, the state machine has been altered. Two extra states, *update T* and *update Tag*, are added between the *loopend1* and *midstate*, and between the *loopend2* and *final* state. These states are 32 cycle loops that flush the pipelined field multiplier, so that the right tag is outputted in the next state. The altered state machine can be seen in Figure 3-12.

Figure 3-12: state machine of the speed optimised code

## 3.3.4 Trivia-ck version 2

In this section, a prototype of the second round Trivia-ck is discussed. As mentioned, this prototype is untested since there is no developer C-code yet. The second version differs from the first in several ways. The first change is in the way the key an npub are loaded into the state. The C part of the state is now loaded with zero's and three "1", instead of all "1". The important change is however the reduction of the intermediary tag to 128-bit instead of 160-bit. This change also removes the use of two different VPVhash blocks, now only VPVhash4 is needed for both tag generation steps. This change decreases the amount of registers considerably. The third change is the way the A and B inputs to the multiplier are formed. Now the key and multiplexer output are divided into four equal parts, and the first and third parts from both are xored to form A, and the second and fourth parts are xored to form B. The final change is that the second keyext output during tag generation (loop1end and loop2end) is multiplied with  $\alpha_{32}$  [18].

Only the reduction of the intermediary tag changes the code in a drastic way. As mentioned, now only one VPVhash block is needed. This also simplifies the insert block, and removes the need to save the keyext outputs, since now the same outputs are used in both tag generation phases. The Trivia-ck prototype is built using the Trivia-ck speed optimised version, so the state machines are the same.

### 3.3.5 Results

Here, the results on area and speed are compared between the different versions of Trivia-ck. Shown below are the result of the area usage, calculated using the ATHENa tool for the basic Trivia-ck code. LUTs are look-up tables and FF's are flip flips. The first results with the full AEAD interface are tested on Spartan and Virtex .

| Device    | LUTS | SLICES | FFs  |

|-----------|------|--------|------|

| Spartan 3 | 5482 | 3116   | 2192 |

| Spartan 6 | 7435 | 2223   | 2321 |

| Virtex 5  | 7491 | 2398   | 2310 |

| Virtex 6  | 7289 | 2093   | 2295 |

Table 3-2: Area results for basic Trivia-ck using AEAD wrapper

However, the results above include the extra hardware of the pre- and postprocessors. In order to truly judge the algorithm for its area usage, it has also been tested without the AEAD wrapper. For this purpose, the Ciphercore wrapper provided by the ATHENa website has been used.

| Device    | LUTS | SLICES | FFs  |

|-----------|------|--------|------|

| Spartan 3 | 5071 | 2959   | 2141 |

| Spartan 6 | 3540 | 1120   | 2002 |

| Virtex 5  | 3407 | 1075   | 1970 |

| Virtex 6  | 3322 | 1399   | 1965 |

Table 3-3: Area usage for basic Trivia-ck without AEAD wrapper

As can be seen, for Spartan 3, the wrapper only uses about 5,04% of the total usage. However in Spartan 6, the usage is 49;61%, for Virtex 5 55,17% and Virtex 6 33,16%. In future results, only the area usage and speed of the algorithm using the Ciphercore wrapper is calculated. Shown below are the results on area usage for both the area optimised and speed optimised versions and Trivia-ck v2.

| Device    | LUTS | SLICES | FFs  |

|-----------|------|--------|------|

| Spartan 3 | 2310 | 1593   | 2282 |

| Spartan 6 | 1775 | 618    | 2113 |

| Virtex 5  | 1974 | 711    | 2132 |

| Virtex 6  | 1724 | 699    | 2112 |

Table 3-4: Area results for area optimised Trivia-ck

| Table 3-5: Area | results for spe | ed optimised Triv | ia-ck |

|-----------------|-----------------|-------------------|-------|

|-----------------|-----------------|-------------------|-------|

| Device    | LUTS | SLICES | FFs  |

|-----------|------|--------|------|

| Spartan 3 | 4823 | 4302   | 7216 |

| Spartan 6 | 4375 | 1405   | 6198 |

| Virtex 5  | 4254 | 1665   | 6166 |

| Virtex 6  | 3981 | 1205   | 6153 |

| Device    | LUTS | SLICES | FFs  |

|-----------|------|--------|------|

| Spartan 3 | 3020 | 2525   | 3980 |

| Spartan 6 | 2572 | 777    | 3365 |

| Virtex 5  | 2760 | 1086   | 3346 |

| Virtex 6  | 2312 | 808    | 3369 |

Table 3-6: Area results for Trivia-ck v2

It can be clearly seen that the area optimised version has the lowest area usage. The speed optimised version has more slices and FF's than the basic version, because of the extra added pipeline registers. The Trivia-ck v2 version sees a significant reduction on area when compared to the speed optimised version, on which it is based. This reduction can be credited to the removal of one of the VPVHash blocks.

Tables 3-7 to 3-10 show the timing results for the basic version, area optimised version, speed optimised version and the second version of Trivia-ck. The place and route (PAR) frequency is the highest clock frequency at which the chip can run the algorithm.

| Device    | PAR Freq (MHz) | Throughput (Mbit/s) | Latency (ns)      |

|-----------|----------------|---------------------|-------------------|

| Spartan 3 | 48,57          | 1554,24             | 988,3+41,1*(M+AD) |

| Spartan 6 | 94,67          | 3029,44             | 507+21,1*(M+AD)   |

| Virtex 5  | 120,57         | 3860,07             | 397,9+16,6*(M+AD) |

| Virtex 6  | 126,41         | 4045                | 379,7+15,8*(M+AD) |

| Device    | PAR Freq (MHz) | Throughput (Mbit/s) | Latency (ns)         |

|-----------|----------------|---------------------|----------------------|

| Spartan 3 | 120,42         | 79,45               | 20993+805,5*(M + AD) |

| Spartan 6 | 149,61         | 98,71               | 16897+648,4*(M + AD) |

| Virtex 5  | 196,97         | 129,96              | 12834+492,5*(M + AD) |

| Virtex 6  | 237,70         | 156,83              | 10635+408,1*(M + AD) |

Table 3-8: Timing results for area optimised Trivia-ck

Table 3-9: Timing results for speed optimised Trivia-ck

| Device    | PAR Freq (MHz) | Throughput (Mbit/s) | Latency (ns)      |

|-----------|----------------|---------------------|-------------------|

| Spartan 3 | 121,12         | 3875,84             | 899,9+16,5*(M+AD) |

| Spartan 6 | 146,59         | 4690,88             | 743,6+13,6*(M+AD) |

| Virtex 5  | 177,49         | 5679,68             | 614,1+11,3*(M+AD) |

| Virtex 6  | 235,07         | 7522,24             | 463,7+8,5*(M+AD)  |

Table 3-10: Timing results for Trivia-ck v2

| Device    | PAR Freq (MHz) | Throughput (Mbit/s) | Latency (ns)  |

|-----------|----------------|---------------------|---------------|

| Spartan 3 | 120,15         | 3846,15             | 907+17*(M+AD) |

| Spartan 6 | 126,89         | 4060,40             | 859+16*(M+AD) |

| Virtex 5  | 150,24         | 4807,69             | 726+13*(M+AD) |

| Virtex 6  | 224,67         | 7189,40             | 485+9*(M+AD)  |

In order to measure the speed of the algorithm, the throughput and the latency are calculated. The throughput of the cipher is the amount of bits per second that are encrypted. The latency is the amount of time it takes for the full message to be encrypted or decrypted. Equation 3-4 shows the method used to obtain the throughput.

$$Throughput\left(\frac{Mbit}{s}\right) = \frac{Blocksize}{latency(N+1,Tclk) - latency(N,Tclk)}$$

Equation 3-4: Throughput calculation [22]

Trivia has a constant block size of 64-bit for all optimisations. The formula in the denominator of Equation 3-4 is the processing time of 1 message block. First the total processing time for N+1 blocks is calculated and the processing time for N blocks is subtracted. This results in the processing time of one block. This processing time needs to be calculated using the amount of clock cycles that are needed to process one block.

Equation 3-4 is used to calculate the throughput for long messages. For short messages, the effective throughput is smaller. The formula for throughput for short messages is found in Equation 3-5. Since the equation for latency is given in Equation 3-7, and for each of the selected candidates the latency per message and AD block is calculated, sufficient information is provided to calculate and compare the throughput of different message sizes. In this thesis, only Equation 3-4 is used to calculate the throughput.

$$Throughput\left(\frac{Mbit}{s}\right)_{Eff} = \frac{N \cdot Blocksize}{latency(N,Tclk)}$$

Equation 3-5: Throughput calculation for short messages [22]

The equation used in calculating the delays can be found below.

$Delay (cycles) = initialisation + tag generation + M processing \cdot \frac{Mlen}{blocksize}$  $+ AD \ processing \cdot \frac{Adlen}{blocksize}$ Equation 3-6 : Delay calculation in cycles

The amount of cycles it takes to process an input depends on several factors. One factor is the AEAD wrapper delay. The code needs to wait until the input, key and IV get updated. The amount of time this takes depends on the length of the inputs and size of the chip IO- buffers. When taking this delay as the absolute minimum, presuming only one clock pulse for each AEAD state, it can be calculated using Equation 3-5:

AEAD delay (cycles) =

$$3 + \frac{Mlen}{64} + \frac{Adlen}{64}$$

Three states: *idle*, *wait\_on\_npub* and *final* are used to input the key, npub and write the tag and need at least 1 clock pulse. *WaitonAD* and *WaitonM* are repeated for every 64 block of input.

The encryption delay is the actual amount of cycles needed process a full message without the AEAD delay. This delay depends on the structure of the state machine and on the message/AD length. For the basic version, it is calculated as following:

encryption delay (cycles) =

$$45 + \frac{Mlen}{64} + \frac{ADlen}{64}$$

(3)

The 45 constant clock cycles are: the loading of the key and IV into the cipher stream (one cycle), two initialisation states (18 cycles each), the *midstate* (one cycle) and two tag generation states (which take three and four cycles respectively). For each 64-bit message/AD block one cycle is needed to process the data.

Thus the total delay is:

total delay (cycles) = AEAD delay + encrytion delay =

$$48 + 2\frac{Mlen}{64} + 2\frac{ADlen}{64}$$

Using the maximum frequency, the amount of cycles/s can be calculated, and thus the delay in ns.

$$latency (ns) = total delay (cycles) \cdot Tclk$$

Equation 3-7: Latency

Now the throughput can be calculated by calculating the latency using Equation 3-7 for N+1 blocks and N blocks, and using the result in Equation 3-4.

In the area optimised version, the encryption delay is calculated as such:

*encryption delay*(*cycles*) =

$$2528 + \frac{Mlen}{64} \cdot (1 + 32 + 64) + \frac{ADlen}{64} \cdot (1 + 32 + 64)$$

And in the speed optimised and second version, it is calculated as following:

encryption delay(cycles) =

$$109 + 2\frac{Mlen}{64} + 2\frac{ADlen}{64}$$

From the results, it can be observed that the speed optimised version has the highest throughput. The PAR frequencies have increased, compared to the basic version, thanks to the pipeline shortening the critical path. Because of this, the throughput has also increased, because the message block processing time has remained the same. Trivia-ck version 2 has a lower throughput because of the more complex multiplier inputs. These results are however untested and are thus susceptible to change. The area optimised version has the highest frequency, being smaller in size allows the components to be placed closer together, shortening the path delays. However, since the latency is high, the actual throughput is low.

Lastly, shown below are the ASIC results using the NanGate PDK 45nm library for all Trivia-ck versions. The area is given in both micron square and gate equivalent (GE), showing the estimated number of gates needed.

Table 3-11: ASIC results for basic Trivia-ck code

| Area (µm <sup>2</sup> ) | Area  | Timing crit | Max Freq | Throughput | Latency (ns)  |

|-------------------------|-------|-------------|----------|------------|---------------|

|                         | (kGE) | path (ns)   | (MHz)    | (Mbit/s)   |               |

| 21049,91                | 26,31 | 4,4264      | 225.92   | 7209,28    | 213+9*(M+ AD) |

| Table 3-12: ASIC | results for Trivia | _ck area optimisation |

|------------------|--------------------|-----------------------|

|                  |                    |                       |

| Area (µm <sup>2</sup> ) | Area<br>(kGE) | Timing crit<br>path (ns) | Max Freq<br>(MHz) | Throughput<br>(Mbit/s) | Latency (ns)     |

|-------------------------|---------------|--------------------------|-------------------|------------------------|------------------|

| 16082,89                | 20,1          | 2,5244                   | 396.13            | 261,37                 | 6382+245*(M+ AD) |

Table 3-13: ASIC results for Trivia\_ck speed optimisation

| Area (µm <sup>2</sup> ) | Area (kGE) | Timing crit | Max Freq | Throughput | Latency (ns)       |

|-------------------------|------------|-------------|----------|------------|--------------------|

|                         |            | path (ns)   | (MHz)    | (Mbit/s)   |                    |

| 63868,20                | 80         | 2,7728      | 360.64   | 11540,7    | 302 + 5,5*(M + AD) |

Table 3-14: ASIC results for Trivia\_ck v2

| Area (µm <sup>2</sup> ) | Area  | Timing crit | Max Freq | Throughput | Latency (ns)  |

|-------------------------|-------|-------------|----------|------------|---------------|

|                         | (kGE) | path (ns)   | (MHz)    | (Mbit/s)   |               |

| 33625,86                | 26,31 | 2,3667      | 422,52   | 13520,64   | 258+8*(M+ AD) |

# 4 Ketje

## 4.1 Algorithm

Ketje is an AE function that is aimed at memory-constrained devices. It relies strongly on nonce uniqueness for security [23]. There are two suggested versions of Ketje: KetjeJr and KetjeSr. Their key, nonce and state sizes can be found in Table 4-1.

| Recommended | Key (bits) | Nonce (bits) | State (bits) | Block length |

|-------------|------------|--------------|--------------|--------------|

| version     |            |              |              | (bits)       |

| KetjeJr     | 96         | 80           | 200          | 16           |

| KetjeSr     | 128        | 128          | 400          | 32           |

Table 4-1: Ketje parameters