# FACULTEIT INDUSTRIËLE INGENIEURSWETENSCHAPPEN

master in de industriële wetenschappen: elektronica-ICT

# Masterproef

2016 • 2017

How to distribute most efficiently a computation intensive calculation on an Android device to external compute units with an Android API

Promotor : dr. Kris AERTS

Promotor : Mr. KUI WANG prof. JARI NURMI

Lander Beckers , Henning Lakiere

Scriptie ingediend tot het behalen van de graad van master in de industriële wetenschappen: elektronica-ICT

Gezamenlijke opleiding Universiteit Hasselt en KU Leuven

# 2016 • 2017 Faculteit Industriële ingenieurswetenschappen master in de industriële wetenschappen: elektronica-ICT

# Masterproef

How to distribute most efficiently a computation intensive calculation on an Android device to external compute units with an Android API

Promotor: dr. Kris AERTS

Promotor: Mr. KUI WANG prof. JARI NURMI

Lander Beckers, Henning Lakiere

Scriptie ingediend tot het behalen van de graad van master in de industriële wetenschappen: elektronica-ICT

## **PREFACE**

This thesis is written in order to complete our master education in electronics and ICT engineering at UHasselt Belgium. The development and writing of this thesis has been done in the Tampere University of Technology, Finland. K. Aerts was the supervisor of our home university, Prof. J. Nurmi and PhD student K. Wang supervised us during the exchange period.

After several meetings with our supervisors we had a solid idea of what the thesis should be about and what the research question should be. We had some major problems with multiple software versions, but thanks to dedicated research and trial and error we were able to fix all of these issues.

We would like to thank our supervisors to contribute in our work and keep us motivated along the whole experience.

Thanks, to all our family members who visited us here in Finland to provide us with some comfort after surviving the cold winter and to all new friends we met here. Without the other exchange students, this experience would not have been this great.

Lander Beckers Henning Lakiere

Tampere, (6th of June 2017)

## **ABSTRACT**

**BECKERS LANDER, LAKIERE HENNING**: Efficient distribution of a computation intensive calculation on an Android device to external compute units with an Android API

Master of Science thesis, 82 pages

6th of June 2017

Major: Embedded Systems

Keywords: Parallel computing, SoC, CPU, FPGA, Android, Bluetooth WebSocket, OpenCL, C++,

Java

#### **Dutch abstract**

Is processor intensieve berekeningen overbrengen naar externe rekeneenheden een nieuwe trend? Deze master thesis onderzoekt of het sneller is om een matrixvermenigvuldiging door te sturen naar en uit te rekenen op een externe rekeneenheid in plaats van direct op de smartphone. Matrices worden via Bluetooth of WebSocket tussen de smartphone en System-On-Chip (SoC) uitgewisseld. De gebruikte rekeneenheid is TerASIC's SoC, uitgerust met een Intel Altera Cyclone V Field Programmable Gate Array (FPGA) en Dual-core ARM A9 processor. Indien de matrices groter zijn dan 1660x1660, dan zal de SoC sneller de matrix vermenigvuldiging kunnen berekenen dan de Android smartphone.

De matrixvermenigvuldiging wordt geaccelereerd in een OpenCL kernel op de FPGA, gestuurd door een in C++ geschreven programma op de processor.

Experimenten toonden aan dat de overdrachtssnelheid van Bluetooth 500 keer trager is dan WebSocket, verdere experimenten zullen dus beter geen Bluetooth implementeren. Matrices groter dan 2338x2338 zijn sneller doorgestuurd, vermenigvuldigt en teruggestuurd op de SoC, dan op de Android smartphone zelf. Verder onderzoek zou andere OpenCL kernels kunnen ontwikkelen die andere berekeningen uitvoeren op niet-vierkante matrices.

#### **English abstract**

Is transferring computation intensive calculations to external compute-units the next trend? This master's thesis researches if it is worth the effort to transfer a matrix multiplication from an Android phone to a System-on-Chip (SoC), using Bluetooth or WebSocket as communication protocols. The SoC solution used in this work is an Intel Altera Cyclone V based board from TerASIC, equipped with a Field Programmable Gate Array (FPGA) including a Dualcore ARM A9 processor. Because the matrix size has a strong correlation to the number of calculations in a matrix multiplication, the calculation time on a CPU and FPGA will differ when the matrices grow in size. Comparing the multiplication times on Android and SoC, matrices with a matrix size above 1660x1660 are calculated faster on the SoC.

The matrix multiplication is accelerated using an OpenCL kernel on the FPGA, guided by a host program on the processor programmed in C++.

Experiments have shown that Bluetooth has a 500 times lower transfer rate than WebSocket, resulting in choosing only WebSocket for further investigations. Due to the transfer times, the minimum matrix size to win time by extending the multiplication to a SoC is 2338x2338. Although the implemented matrix multiplication does only support square matrices, future research could develop multiple kernels of different algorithms that support a variation in width and height.

| Authors' Contributions   |                               |         |

|--------------------------|-------------------------------|---------|

| Chapter                  | Section                       | Author  |

| Poster                   |                               | Lander  |

| Abstract                 |                               | Lander  |

| Preface                  |                               | Henning |

| 1 Introduction           |                               | Lander  |

| 2 Theoretical background | 2.1 Matrix multiplication     | Lander  |

|                          | 2.2 Parallel computing        | Henning |

|                          | 2.3 Smartphone                | Henning |

|                          | 2.4 Communication             | Henning |

|                          | 2.5 SoC                       | Lander  |

| 3 Implementation         | 3.1 Communication protocol    | Henning |

|                          | 3.2 SoC                       | Lander  |

|                          | 3.3 Android Apps              | Henning |

| 4 Results                | 4.1 OpenCL performance        | Lander  |

|                          | 4.2 Phone performance         | Henning |

|                          | 4.3 Bluetooth vs WebSocket    | Henning |

|                          | 4.4 Conclusion of the results | Lander  |

| 5 Conclusion             |                               | Lander  |

# **CONTENTS**

| Pr | eface    |                                      | i  |

|----|----------|--------------------------------------|----|

| 1. | Introduc | ction                                | 1  |

| 2. | Theoreti | ical background                      | 3  |

|    | 2.1 Ma   | atrix multiplication                 | 3  |

|    | 2.2 Par  | rallel computing                     | 4  |

|    | 2.2.1    | What is parallel computing           | 4  |

|    | 2.2.2    | Classification of parallel computing | 6  |

|    | 2.2.3    | OpenCL                               | 7  |

|    | 2.3 Sm   | nartphone                            | 8  |

|    | 2.3.1    | Android OS                           | 9  |

|    | 2.3.2    | Android Studio                       | 9  |

|    | 2.4 Con  | mmunication                          | 9  |

|    | 2.4.1    | Bluetooth                            | 10 |

|    | 2.4.2    | WebSocket                            | 14 |

|    | 2.5 So(  | C                                    | 18 |

|    | 2.5.1    | Hard Processing System               | 19 |

|    | 2.5.2    | FPGA                                 | 28 |

|    | 2.5.3    | Bridges                              | 34 |

|    | 2.5.4    | Quartus                              | 36 |

| 3. | Impleme  | entation                             | 41 |

|    | 3.1 Con  | mmunication protocol                 | 41 |

|    | 3.1.1    | Bluetooth communication protocol     | 42 |

|    | 3.1.2    | WebSocket communication protocol     | 44 |

|    | 3.2 So(  | C                                    | 45 |

|    | 3.2.1    | Websocket                            | 46 |

|    | 3.2.2    | Bluetooth on the HPS                 | 48 |

|    | 3.2.3    | Bluetooth on the FPGA                | 52 |

|                  | 3.2.4      | OpenCL host                                                                             | 56 |

|------------------|------------|-----------------------------------------------------------------------------------------|----|

|                  | 3.2.5      | OpenCL kernel                                                                           | 57 |

| 3.3 Android apps |            | droid apps                                                                              | 60 |

|                  | 3.3.1      | Matrix multiplication                                                                   | 60 |

|                  | 3.3.2      | Bluetooth application                                                                   | 62 |

|                  | 3.3.3      | WebSocket application                                                                   | 65 |

| 4.               | Results .  |                                                                                         | 69 |

|                  | 4.1 Ope    | enCL performance                                                                        | 69 |

|                  | 4.1.1      | Global memory sum storage                                                               | 70 |

|                  | 4.1.2      | Local memory sum storage                                                                | 71 |

|                  | 4.1.3      | Global to local memory copy                                                             | 71 |

|                  | 4.1.4      | Global memory sum storage on the MacBook Pro                                            | 72 |

|                  | 4.1.5      | Comparison between matrix multiplications on different architectures in Java and OpenCL | 73 |

|                  | 4.2 Pho    | one performance                                                                         | 74 |

|                  | 4.2.1      | Matrix multiplication                                                                   | 74 |

|                  | 4.2.2      | Bluetooth app                                                                           | 74 |

|                  | 4.2.3      | WebSocket app                                                                           | 75 |

|                  | 4.3 Blu    | etooth vs WebSocket communication speed                                                 | 76 |

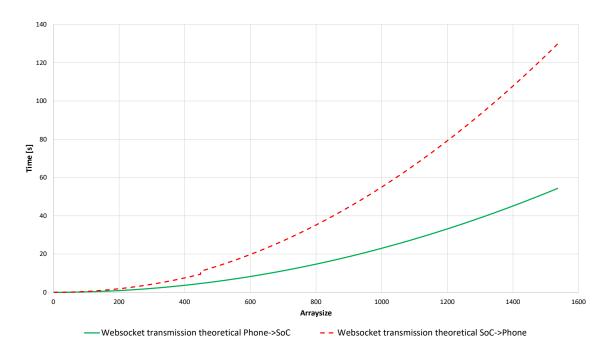

|                  | 4.3.1      | WebSocket transmission                                                                  | 77 |

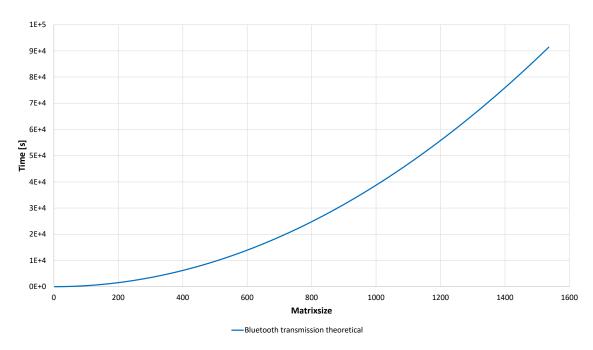

|                  | 4.3.2      | Bluetooth transmission                                                                  | 77 |

|                  | 4.3.3      | Bluetooth vs. WebSocket                                                                 | 78 |

|                  | 4.3.4      | WebSocket and SoC vs. Android smartphone                                                | 79 |

|                  | 4.4 Cor    | nclusion of the results                                                                 | 80 |

| 5.               | Conclusion | on                                                                                      | 81 |

| Bi               | bliography | y                                                                                       | 83 |

# LIST OF FIGURES

| 2.1  | Workflow serial computing                                                                           | 5  |

|------|-----------------------------------------------------------------------------------------------------|----|

| 2.2  | Workflow parallel computing                                                                         | 5  |

| 2.3  | Four possible classifications according to Flynn's Taxonomy                                         | 6  |

| 2.4  | Architecture classes from Flynn's taxonomy                                                          | 7  |

| 2.5  | Piconets and Scatternets                                                                            | 11 |

| 2.6  | Bluetooth protocol stack                                                                            | 12 |

| 2.7  | WebSocket handshaking                                                                               | 15 |

| 2.8  | Standard WebSocket dataframe format                                                                 | 16 |

| 2.9  | Layout of the DE1SoC development board of TerASIC                                                   | 19 |

| 2.10 | Cyclone V Hard Processing System layout                                                             | 20 |

| 2.11 | Compilation process from High level programming language to an executable file [17]                 | 22 |

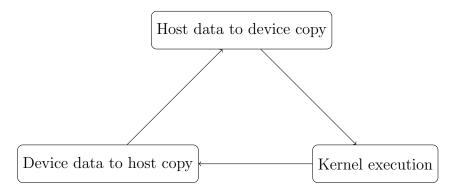

| 2.12 | 2 OpenCL real life applications kernel cycle                                                        | 28 |

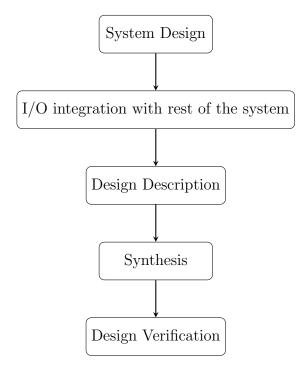

| 2.13 | FPGA design flow                                                                                    | 29 |

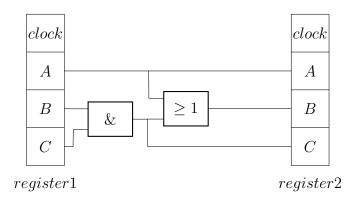

| 2.14 | HDL races figure                                                                                    | 31 |

| 2.15 | OpenCL kernel representative school layout                                                          | 34 |

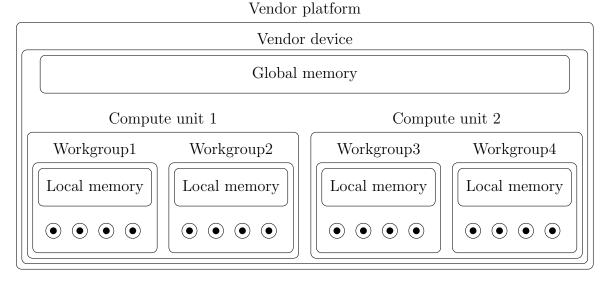

| 2.16 | S OpenCL kernel layout: The circles represent work items with a dot in the middle as private memory | 34 |

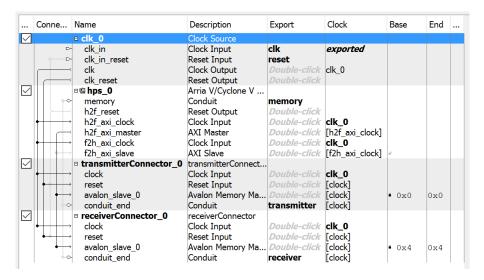

| 2.17 | Qsys internal connections                                                                           | 37 |

| 2.18 | Qsys configuration of bridges                                                                       | 37 |

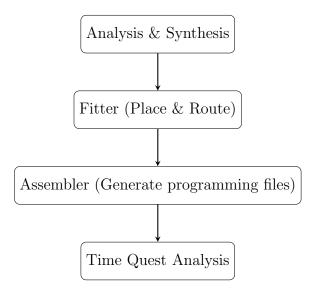

| 2.19 | FPGA design flow                                                                                    | 38 |

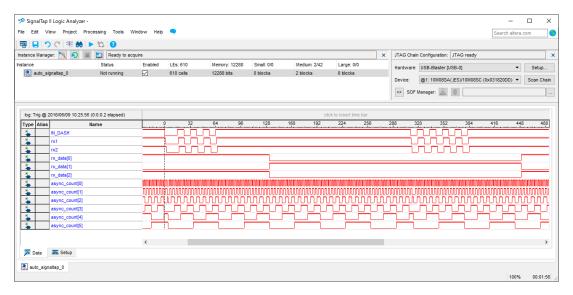

| 2.20 | SignalTap II Logic Analyzer layout                                                                  | 39 |

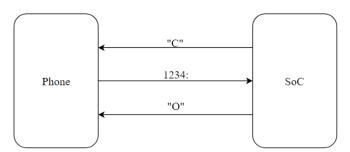

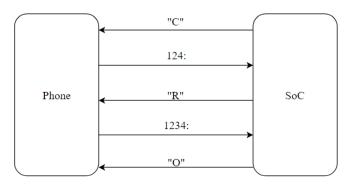

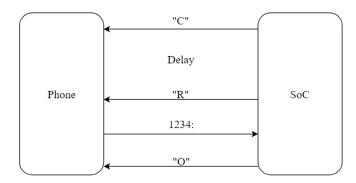

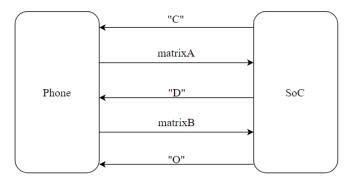

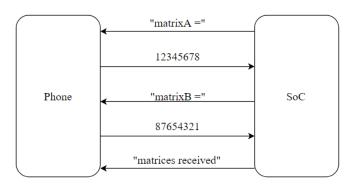

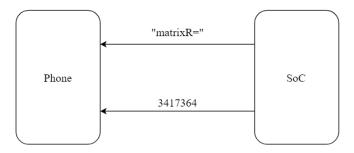

| 3.1  | Correct message transfer                                                                                                         | 42 |

|------|----------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2  | Incorrect message transfer                                                                                                       | 43 |

| 3.3  | Delayed message                                                                                                                  | 43 |

| 3.4  | Switch matrix message                                                                                                            | 43 |

| 3.5  | Sending matrix A and B                                                                                                           | 45 |

| 3.6  | Sending result matrix                                                                                                            | 45 |

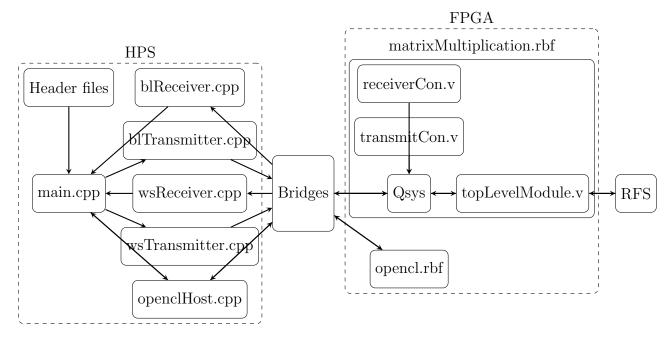

| 3.7  | Block diagram of the implemented system on the SoC with both the HPS and FPGA modules                                            | 47 |

| 3.8  | Graphical programming layout of the system in Qsys                                                                               | 55 |

| 3.9  | Matrix multiplication app                                                                                                        | 61 |

| 3.10 | Bluetooth menu                                                                                                                   | 61 |

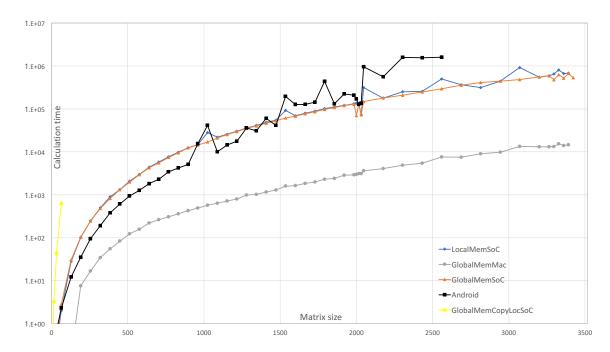

| 4.1  | Comparison between OpenCL kernel and Android matrix multiplication calculation times. The vertical axis is in logarithmic scaled | 70 |

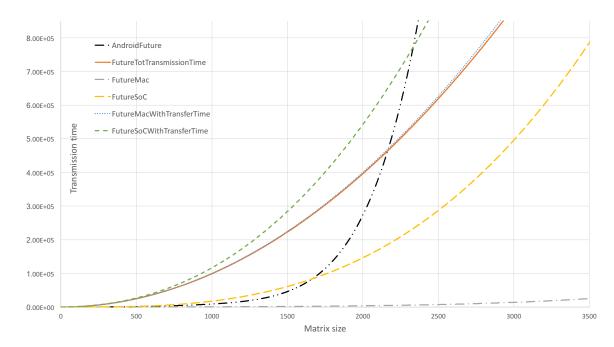

| 4.2  | Comparison between matrix multiplications on different architectures, with and without the matrix transportation time            | 73 |

| 4.3  | Result screen matrix multiplication                                                                                              | 75 |

| 4.4  | CPU and RAM usage                                                                                                                | 75 |

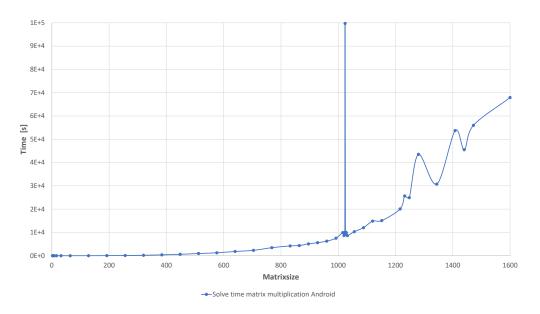

| 4.5  | Results for Android matrix multiplication                                                                                        | 75 |

| 4.6  | CPU and RAM usage Bluetooth                                                                                                      | 76 |

| 4.7  | Bluetooth app log                                                                                                                | 76 |

| 4.8  | WebSocket app log                                                                                                                | 76 |

| 4.9  | RAM, network and CPU usage WebSocket                                                                                             | 77 |

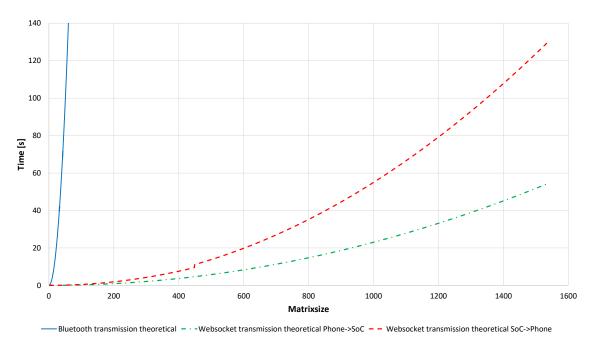

| 4.10 | WebSocket transmission time for phone to SoC and vice versa                                                                      | 78 |

| 4.11 | Bluetooth transmission time                                                                                                      | 78 |

| :  | : | : |

|----|---|---|

| XI | 1 | ı |

|    | _ | _ |

| 4.12 Bluetooth transfer time vs. | WebSocket transfer time | <br>79 |

|----------------------------------|-------------------------|--------|

|                                  |                         |        |

# LIST OF TABLES

| 3.1 | OpenCL kernel: matrix multiplication implementation flow table with matrix-Size equal to two | 59 |

|-----|----------------------------------------------------------------------------------------------|----|

| 4.1 | Resource usage in global memory implementation                                               | 71 |

| 4.2 | Resource usage in local memory implementation                                                | 71 |

| 4.3 | Resource usage global to local memory copy implementation for 128 x 128 matrices             | 72 |

| 4.4 | Resource usage global to local memory copy implementation for 64 x 64 matrices               | 72 |

# LIST OF ABBREVIATIONS

ASIC Application-Specific Integrated Circuit

CAD Computer Aided Design CPU Central Processing Unit

DDR Double Data Rate

FPGA Field Programmable Gate Array

GPIO General Purpose Input Output

GPU Graphical Processing Unit

GUI Graphical User Interface

HDL Hardware Description Language HPS Hardware Processing System

IP Intellectual PropertyIC Integrated CircuitOS Operating SystemPCB Printed Circuit Board

SDRAM Synchronous Dynamic Random Access Memory

SoC System on Chip SOF SRAM Object File

UART Universal Asynchronous Receiver Transmitter

Verilog Is a HDL like VHDL, but with a different syntax

VHDL VHSIC Hardware Description Language

VLSI Very Large Scale Integration

#### 1. INTRODUCTION

Since Baron J.J.B discovered silicon in 1823, 125 years passed by before the first transistor was created. Transistors are the main components in all electronic circuits. It took another 25 years to publish the first microprocessor, named Intel 4004. The 4-bit Intel 4004 was able to perform 60.000 operations per second and was built with 2300 transistors. Five years earlier, in 1965, Gordon E. Moore made a statement in a paper [10], called "Moore's law". Moore's law is now a computing term, specifying that the number of transistors available on an integrated circuit doubles every two years. 50 years after he published his paper, his law is still standing. Every year since, processors kept increasing their clock frequency, internal memory and register width. The register width of the Intel 4004 was 4 bits. 4 bits increased to 8, 16, 32 and nowadays commercial available 64-bit architectures.

Ten years after the first commercial processor, Intel 4004 [14], was released, the first Field Programmable Gate Arrays (FPGAs) were created [35]. They where difficult to program, expensive and had a small amount of configurable logic blocks. Most designers avoided them and used processors and/or ASICs. ASICs are Application-Specific Integrated Circuits, designed for a specific purpose. When the application required parallel data processing, ASICs were used. Disadvantage of ASICs are the high initial production costs and difficult development. Although these days FPGAs have more logic blocks than ASICs and are partially reconfigurable after final configuration, ASICs are still used in high mass productions.

A next step in the evolution could be a combination of both Central Processing Unit (CPU) and FPGA. CPUs are amazingly stable, cheap and it is easy to develop programs for execution. FPGAs on the other hand are relative more expensive, more difficult to configure and consume more energy than comparable CPUs. Although right now you might think that CPUs are better than FPGAs, FPGAs have one advantage above all CPUs: they can massively process data in parallel. There exists something in-between, called a Graphical Processing Unit (GPU). GPUs differ from FPGAs with their fixed internal configuration and are able to compute the same instruction on multiple data. More about this can be found in 2.2: Parallel computing.

The following questions must be answered in this thesis, in order to answer our research question: "How to most efficiently distribute a computation intensive calculation on an Android device to external compute units with an Android API?". During this thesis a matrix mul-

tiplication from an Android phone is transferred to a System-on-Chip (SoC). The used SoC in this thesis is TerASICs DE1SoC, equipped with an Intel Altera Cyclone V FPGA and a Dual-core ARM A9 processor. The main purpose of extending this calculation to a SoC, is achieving a faster matrix multiplication result. The most interesting question will be: can a matrix multiplication, extended to a SoC, calculate a faster result than a multiplication on the Android device and/or at which matrix size is it profitable? Other interesting questions are, which communication protocol will be the most reliable and fastest to exchange matrices with the SoC. We will implement two communication protocols, Bluetooth and WebSocket.

This thesis comprises three chapters: Theoretical background, Implementation and Results. Firstly, we will describe which knowledge and resources are used to develop the programs for the SoC and the Android application. Secondly, the complete implementation is explained in depth. Beginning with the character error detection algorithm, this algorithm is mandatory to ensure zero package loss during Bluetooth communication. There are two other parts in this chapter: SoC and Android. Section SoC implements both Hard Processor System (HPS) and FPGA systems. The HPS is used as a host to start everything: receiving, calculating in OpenCL and receiving with both Bluetooth and WebSocket as communication protocols. During the calculations or when Bluetooth is used, the FPGA needs to be programmed and accessed from HPS. All calculations are performed by OpenCL on the FPGA side of our SoC. Android is our "customer", if a matrix calculation needs to be processed, then the Android application can connect to the SoC and transfer the matrix multiplication. Thirdly, we will discuss the results in chapter "results". We consider two questions useful to solve this thesis's problem. How does the OpenCL calculation perform compared to a single threaded CPU? The basic step is to verify if OpenCL is able to accelerate the matrix multiplication, otherwise our research question is already unfeasible. Afterwards, the communication to share the matrices has to be quick enough to ensure a faster result matrix on the Android. When the total matrix transmission times added with the OpenCL calculation time is larger than the single treaded matrix multiplication on Android, then already a final conclusion is achieved. The last chapter "Conclusion" will respond to all questions asked in this paragraph.

## 2. THEORETICAL BACKGROUND

All used knowledge and resources are explained in depth in this chapter. The basic matrix multiplication algorithm is explained in section 2.1 and a basic analysis is made to count the number of calculations depending on the matrix size. In the next section 2.2 describes and classifies parallel computing. In 2.3 is discussed how an Android application is compiled, developed and executed. Next, sections 2.4.1 and 2.4.2 explain respectively the basics of Bluetooth and WebSocket communication. Every component of the matrix multiplication accelerator "SoC" can be found in section 2.5, those components are the HPS, the FPGA and the bridges between the two combined with the development software used.

# 2.1 Matrix multiplication

Before explaining why we have chosen a matrix multiplication as a computation intensive algorithm, we will show how matrices A and B are multiplied in equation 2.1 [34].

$$\begin{bmatrix} 1 & 2 \\ 3 & 4 \end{bmatrix} \times \begin{bmatrix} 5 & 6 \\ 7 & 8 \end{bmatrix} = \begin{bmatrix} 1 \times 5 + 2 \times 7 & 1 \times 6 + 2 \times 8 \\ 13 \times 5 + 4 \times 7 & 3 \times 6 + 4 \times 8 \end{bmatrix} = \begin{bmatrix} 19 & 22 \\ 93 & 50 \end{bmatrix}$$

(2.1)

This is the most common method to multiply two matrices and it works in every situation. When a calculation is complex, people tend to divide the problem into a number of multiple smaller/easier problems. Using matrices to describe functions is one of those easier ways to deal with real life problems. That is the reason why most common tools in engineering use matrices. The numbers in a matrix represent the data from measurements or approximations given by mathematical equations. In many time-sensitive applications a faster method to solve matrix calculations could give faster approximations for real life problems [11]. We needed to choose a specific matrix calculation to implement and have set the shape of the matrices as square. The reason why we have chosen a matrix multiplication is concluded from equation 2.2. This equation clearly shows that the number of calculations grows faster than the matrixSize to the power of 3. By parallelizing, all calculations are placed in parallel, resulting in a bigger throughput.

$$numberOfCalculations = (2 \times size - 1) \times size^{2}$$

(2.2)

$$M = \begin{bmatrix} A & B \\ \dots & \dots \end{bmatrix} \tag{2.3}$$

$$N = \begin{bmatrix} F & \dots \\ G & \dots \end{bmatrix} \tag{2.4}$$

$$R1 = \begin{bmatrix} A \times F + B \times G & \dots \\ \dots & \dots \end{bmatrix}$$

(2.5)

This is how we derive equation 2.2. First, the number of calculations when calculating the first element of the result matrix R1 are counted. When processing the matrix multiplication M x N a count of three calculations, i.e. one addition and two multiplications, is achieved. After processing the same calculation for a matrix with size five, the result matrix R2 in equation 2.6 will be calculated. Result matrix R2 contains 4 additions and 5 multiplications for each element, resulting in 20 (4 x 5) calculations. The number of calculations for one element in the result matrix is always equal to "number of additions" added with "number of multiplications" and the number of elements in a result matrix are equal to matrixSize x matrixSize. When those are combined in a formula, this results in equation 2.2.

## 2.2 Parallel computing

Parellel computing has made an uprising in the last couple of decades. Due to some technology constraints developers moved to multicore processors. This is not the only way of parallel computing, but more will be explained in the next sections.

# 2.2.1 What is parallel computing

The problem when facing large calculations is that they require a lot of computing power and thus time. Performing these calculations can be done with two types of computation, serial

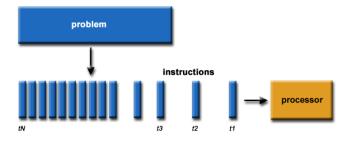

and parallel computing. Serial computing means, you have one compute unit (e.g. a single-core CPU) available that performs all instructions on a certain set of data. This set of data will be broken into multiple smaller subparts that will be solved by a certain instruction. The single compute unit performs the instruction on every subpart in order to solve the whole part as shown in figure 2.1 [8].

Figure 2.1 Workflow serial computing

Parallel computing, on the other hand, is the simultaneous use of multiple compute units, or a compute resource, to solve a computational problem. This compute resource can be a CPU with multiple cores, a combination of a CPU with different compute accelerators such as a GPU or even a whole network of computers and servers. We break the main problem into smaller subproblems as we did with serial computing. Now, since there are multiple compute units, we can distribute the subproblems among all these compute units. Every unit can now perform an instruction on their given subproblem simultaneously as shown in figure 2.2. With multiple

Figure 2.2 Workflow parallel computing

compute units executing one task, we will shorten the completion time and even have a potential cost saving. It also allows us to solve larger/complex problems since a single computer could suffer from limited memory. And last, we are able to access non-local resources in a network that would not be accessible from a local computer.

It is easy to conclude that the concept of parallel computing was to have a more efficient way to handle large sets of data such as huge databases, images or simulations that involve large

datasets. It is also easier to deal with complex data for example algorithms [8].

## 2.2.2 Classification of parallel computing

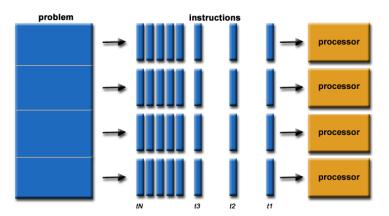

Parallel computing systems can be separated into different classes. According to Flynn's taxonomy, we can roughly place any of these systems in one of the four classes. This classification was first studied by Michael Flynn in 1972 [3]. The classifications are determined by two factors: instruction stream and data stream which both have two possible states being single or multiple. Figure 2.3 represents a the four possible classes from the Flynn's taxonomy [8].

Figure 2.3 Four possible classifications according to Flynn's Taxonomy

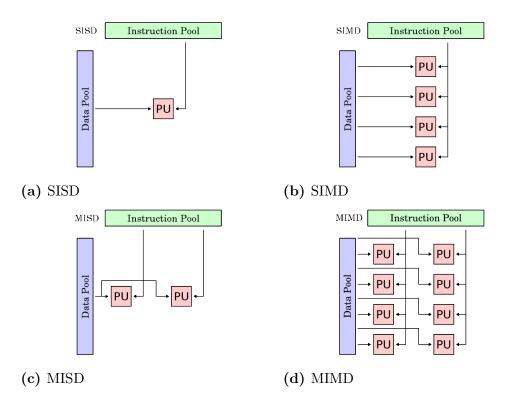

#### • SISD

The SISD class will have a single core processor executing a single data stream to operate on data stored in a single memory (figure 2.4a). This means that a parallel compute system cannot be classified as an SISD system, but Flynn's taxonomy was not made for just classifying parallel compute systems. Any traditional single-core processor falls into this category but it is usually old computers or older compute units that can be classified as SISD.

#### • SIMD

Data is distributed amongst multiple processors who all execute the same instruction on this data (figure 2.4b). Since we have access to multiple compute units, parallel computing can be categorized in this class. Furthermore, this is the class where we can categorize our subject of the thesis in since we have a large set of data divided over multiple data streams (MD) and only one instruction stream (SI) since all processing units will perform the same instruction on the data. The SIMD class contains the most modern computers, particularly those with a graphics processor unit (GPU).

#### • MISD

Each processing unit operates on the data independently via separate instruction streams while a single data stream is fed into multiple processing units (figure 2.4c). This class knows very few applications. An example of an application is the use of multiple cryptography algorithms attempting to crack a single coded message.

#### • MIMD

This time every processing unit is able to execute a different instruction stream on a different data stream (figure 2.4d). This means that any instruction can be applied on any data package for every compute unit. Most supercomputers, networked parallel computer clusters and "grids" can be classified as a MIMD compute system. Also, many MIMD architectures include SIMD execution sub-components.

Figure 2.4 Architecture classes from Flynn's taxonomy

# 2.2.3 OpenCL

Companies worldwide constantly strive to improve computational performance. They start using GPUs, FPGAs and other compute accelerators that behave as a coprocessor to process

parallel workload. In order for these heterogeneous architectures to function properly, we need software that supports heterogeneous computing on hardware platforms from different vendors. To make this possible, developers use toolkits such as Threading Building Blocks (TBB), OpenMP, Compute Unified Device Architecture (CUDA), and others [29]. However, some of the existing toolkits were limited to either only being able to use a single microprocessor family or they did not support heterogeneous computing. OpenCL on the other hand provides a set of easy-to-use abstractions and a wide variety of APIs. OpenCL was developed by the Khronos group as a parallel computing API for Apple's OS X release of Snow Leopard back in 2009. This Khronos group is a mixture of people from different hardware vendors like ATI technologies, Intel, Nvidia to name a few [2].

One of the main reasons companies start using OpenCL is that in the past they would use GPUs, when they should be using FPGAs while others had the problem the other way around. The problem they had is that converting CUDA, which is the parallel computing platform from Nvidia (GPUs), to VHDL is difficult and annoying to do. More reasons on why OpenCL should be used to program FPGAs are listed below [22].

# • Simplicity and ease of development Because most software developers are more familiar with C than low-level HDL language, OpenCL is easy to understand for the vast majority of developers worldwide.

#### • Code profiling

OpenCL allows you to determine where exactly the performance-sensitive pieces in your code are. This way it is easy to assign these pieces of code to be executed by hardware accelerators as kernels.

#### • Performance & Efficiency

Every developer wants to have his software build in the most efficient way to benefit from maximum performance. Due to the FPGA's parallelistic architecture, you only need to generate the logic the device needs to run the software to deliver high performance.

#### • Code reuse

Since there are multiple devices that are supported by OpenCL, you can reuse your already written code on almost any of the other devices without having to change a thing.

# 2.3 Smartphone

Nowadays, almost everyone has a smartphone. These portable computers allow us to communicate with anyone across the world from almost any place. They can be used as entertainment devices to play music or video games and over the last couple of years even services like stock markets or banking systems have been integrating with smartphones. Furthermore, you can

make pictures with them, view all sorts of media, and the list goes on. Since the increasing popularity there have been many companies developing smartphones. The most common brands are Samsung and Apple accounting for over 37% of the market shares in 2017 of all smartphone brands [24].

#### 2.3.1 Android OS

Like most communication devices, smartphones need an operating system (OS). While Apple's IPhones use their own OS called iOS, Samsung and many other smartphone manufacturers use the Android OS that was developed by Google. With a whopping 81,7% worth of market shares at the end of 2016, Android is definitely one of the market leaders when it comes to smartphone operating systems [15].

One of the main features of smartphones are applications or apps in short. Google's Play Store has over a million apps available for almost any Android device. Unlike Apple's App Store, basically anyone can upload their own apps on Google's Play Store. To upload apps as a developer for everyone to download and use you pay a one-time fee of 25\$ to Google. Making apps on the other hand is free. Most apps are written in Java and there are multiple integrated development environments (IDE) available for the Android platform. The official IDE for Android is Android Studio which is described in the next section. Other IDEs available are AIDE (HTML, C, C++), Xamarin (C#) and many others.

#### 2.3.2 Android Studio

Android Studio is the official IDE where you can develop apps for phones with an Android OS. Its main programming language is Java but since Android Studio version 2.2 it is possible to write and use C and C++ code by compiling it into a native library. With the Java Native Interface (JNI) you can call the C/C++ functions in your native library. Furthermore, Android Studio splits up front and back end of the application giving the developer a nice clean overview of the whole project. The front end can be edited through coding or with a visual interface where you can pick and place your required objects in a layout. The front end design is an xml-file that is attached to an activity. This activity is part of the back end where you write your code in order to interact with the front end of the application.

#### 2.4 Communication

Communication in computer science is an act of exchanging information between two or multiple devices. It requires at least one sender, a receiver, a medium and a set of rules called a protocol. The next sections will briefly discuss some properties of the two mediums that were used for this thesis: Bluetooth and WebSocket.

#### 2.4.1 Bluetooth

Bluetooth is a form of wireless communication that was developed in 1994 by Ericsson Mobile in Sweden. It is a radio frequency (RF) technology using the 2.4GHz industrial, scientific and medical (ISM) band, the same band where you can find ZigBee and WiFi aswell. It can be used to transmit data or voice communication over short distances. Bluetooth radios can be found in nearly every new smartphone and laptop device. It is easy to use, to setup and it has a lot of applications, for example hands-free devices, home heating systems, entertaining devices and so on. Bluetooth is designed to be low cost, for about 5-10\$ per unit. The down side of this is the short connection range and the limited transmission speed of around 780 kb/s [26].

#### Bluetooth benefits

The introduction of Bluetooth allowed for many new applications in several areas. Even today it is still widely used, mostly for multimedia devices, keyboards, mices, printers. The following list explains some benefits for three general areas:

**Data and voice acces points.** Bluetooth allows a wireless connection between devices through which they can communicate. With Bluetooth, the devices are able to transmit voice and data packages in real-time.

Cable replacement. Some wired connections between devices require special cables or adapters. Bluetooth eliminates this hassle since any device can connect to another with the right communication protocol. The range of this connection is approximately 10m and doesn't require the devices to be in line of sight. With an optional amplifier the range can be extended to 100m.

**Ad hoc networking.** Devices with a Bluetooth radio can establish instant connections with each other as soon they come into range.

#### Master, slave and piconet

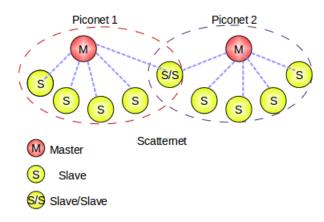

For a Bluetooth connection to exist, there has to be at least one master and one slave device. They use what is called the master/slave model. A master device can be connected to up to seven slave devices while a slave can only connect to one master device. A network of one master and one to seven slaves is called a piconet. The master device will coordinate all the

communication throughout the piconet. All slave devices are allowed to exchange data with the master device when granted premission, but cannot communicate with other slaves in the piconet. The connection between each device is encoded and protected to prevent other devices from eavesdropping and to prevent interference between other devices. Furthermore, in order for these devices to connect with each other, they require the same communication protocol. A device in one piconet can also exist as part of another piconet and can function as either a slave or a master in each piconet. This form of overlapping is called a scatternet [28]. An example of two piconets forming a scatternet is shown in figure 2.5.

Figure 2.5 Piconets and Scatternets

The piconet/scatternet allows the devices to share the same physical area, allowing the network to make efficient use of the bandwidth. A Bluetooth system can use up to 79 different frequencies using a frequency hopping (from 2.402 to 2.480 GHz) [25] scheme with a carrier spacing of 1MHz. This allows a bandwidth of 80MHz. Without frequency hopping scheme, every single channel would have a bandwidth of 1MHz at their disposal. With frequency hopping, the sequence will define a logical channel. This allows to have an available bandwidth of 1MHz at any given time, with a maximum of eight devices sharing the bandwidth. This 80 MHz bandwidth can be shared by several different logical channels. Though, this can cause signal collisions when devices in different piconets, on different logical channels have the same hop frequency at a given time. Signal collisions degrade the performance, so we can state that the more piconets we have, the more collisions occur, the lower our total performance will be [28].

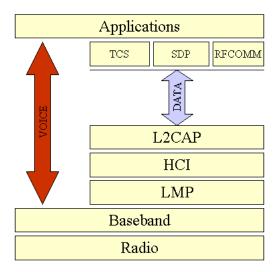

#### Protocol architecture

The Bluetooth protocol architecture consists of four basic layers: core protocols, cable replacement, telephony control protocols and adopted protocols. Figure 2.6 shows the architecture of the Bluetooth protocol stack.

Figure 2.6 Bluetooth protocol stack

**Core protocols.** The core protocol is a five-layer stack. Every layer in the stack has its own responsibilities that are mentioned below.

- The *radio* layer is the wireless connection that specifies certain details about the air interface, including frequency, the use of frequency hopping, modulation scheme and transmit power.

- The baseband layer is responsible for the packet transmission to the radio layer. As mentioned before this data can contain data or voice packages. For the data packages, asynchronous connectionless (ACL) links are used while voice packages are transmitted with synchronous connection-oriented (SCO) links. The baseband layer maintains both ACL and SCO links. It is important for data packages to be transmitted correctly to maintain data integrity, while it is not a problem in case some voice packages get lost. That is why SCO packages are never retransmitted. If you would retransmit voice packages, every next package would suffer from a time delay restraining us from having real-time communication.

- The *Link manager protocol (LMP)* uses the links setup by the baseband and manages the connection between Bluetooth devices. Furthermore, it is responsible for monitoring service quality, security aspects such as device authentication, encryption plus the control and negotiation of baseband packet sizes.

- The Host controller interface (HCI) is the layer between the hardware and the software. The L2CAP layer and the layers above it are implemented in the software while all other layers under the HCI (LMP, baseband, radio) are part of the hardware. The HCI driver acts as a physical bus that connects the hardware with software. It is possible to access

the L2CAP layer directly by the application making it easier for application programmers. This makes the HCI, in some cases, an unnecessary component.

- The Logical link control and adaptation protocol (L2CAP) receives application data and transforms this to the Bluetooth format. Furthermore, Quality of Service (QoS) parameters are exchanged at this layer [25].

- According to [25], the Service discovery protocol (SDP) is not a part of the Core protocols. Though, it contains all the information, services and charasteristics in order to establish a connection between two or more Bluetooth devices. The LMP uses the SDP's first to find out what services are available from the access point. Then information from the SDP is obtained by the LMP to create a L2CAP channel.

Cable replacement. The RFCOMM seen in figure 2.6 is the cable replacement protocol. It is a virtual serial port that is designed to replace cable technology. Serial ports are common types of communication interfaces used with computing and communication devices [28]. So with RFCOMM we eliminate the need for serial ports for communication between two devices, assuming both are equiped with a Bluetooth radio. EIA-232, once known as RS-232, is a widely used serial port interface standard. The RFCOMM will provide binary data transport and has to emulate EIA-232 control signal to the baseband layer.

**Telephony control protocols.** Telephony control specifications (binary) or TCS BIN, is a bit-oriented protocol that is necessary to define the call control services in order to establish speech or data calls between the Bluetooth devices.

Adopted protocols. Adopted protocols are protocols developed by other organizations. They are "adopted" into the overall Bluetooth architecture. They are usually standard protocols well known in applications other than Bluetooth. Bluetooth's strategy is to only invent necessary protocols and use existing standard protocols whenever possible. The following standards are the adopted protocols:

- The *PPP*, or point-to-point protocol is as a internet standard protocol for transporting IP datagrams over point-to-point links.

- TCP/UDP/IP, are the foundation protocols of the TCP/IP protocol suite.

- The object exchange protocol, or OBEX, is a session level protocol made by the Infrared Data Association (IrDA). It is used for exchaning objects. OBEX comes with quite similar

funcionalities as HTTP, but in a simpler way. There is also a model included in OBEX that is used for the representation of objects and operations.

• Bluetooth also adopts the wireless application environment WAE and the wireless application protocol WAP into its architecture.

#### 2.4.2 WebSocket

WebSocket are used for fast, real-time communication between a server and a client. The HTTP model, which is also a communication protocol between a server and a client, allowed the client only to request data from the server, while the server was only able to fulfill these requests. WebSocket on the other hand, allow bidirectional communication between the server and the client. This means both client and server can request data and also respond to these requests. The main point of webSocket is to have true concurrency and to focus on the optimization of performance when it comes to communication and exchanging data. The WebSocket protocol that will be discussed is also known as the RFC6455 model [21].

#### WebSocket communication

Handshake. To communicate over WebSocket, the server and the client first have to connect with each other. The establishment of a WebSocket connection is done by a WebSocket handshake. Handshaking is the exchange of information between two devices and the agreement about which protocol will be used to exchange data after the connection is established. A well known example of this is the TCP three-way-handshake. The client sends a synchronization message (SYN) to the server as a request to synchronize with the server. If the server receives this message and allows the client to synchronize with it, it will send a similar SYN message and an acknowledgement message (ACK) to let the client know that it has received the request. When the client receives the SYN-ACK message, it will send an ACK message back to the server to acknowledge that it has received the server's message. The TCP connection is established whenever the server receives the ACK message from the client.

The WebSocket handshake is quite similar. The client sends a handshake request to the server, and the server will respond with a similar handshake request as seen in figure 2.7. The desktop, smartphone and tablet in figure 2.7 represent the clients that are connected to the server. The handshake request from the client-side is shown in program 2.1, while the response from the server is shown in program 2.2.

Program 2.1, the handshake request from the client, is a pretty standard HTTP request. It is built with multiple headers, some of which are mandatory for the request to be valid. If one of the headers is not understood, the server will reply with "400 Bad Request" and it will

Figure 2.7 WebSocket handshaking

1 GET /chat HTTP/1.1

2 | Host: example.com:8000

3 | Upgrade: websocket 4 | Connection: Upgrade

$5 \mid Sec-WebSocket-Key: dGhlIHNhbXBsZSBub25jZQ =$

6 | Sec-WebSocket-Version: 13

Program 2.1 Client's request for WebSocket handshake

close the socket afterwards. In some cases, it will also give a reason why the handshake failed, although browsers do not display these messages. If there is a problem with version numbers, the server adds a "Sec-WebSocket-Version" header in the HTTP response that contains the version it understands [23]. When the server receives a request handshake from a client with all

1 HTTP/1.1 101 Switching Protocols

2| Upgrade: websocket

3 Connection: Upgrade

4 | Sec-WebSocket-Accept: s3pPLMBiTxaQ9kYGzzhZRbK+xOo=

5

Program 2.2 Server's response for WebSocket handshake

the necessary headers, it will reply with a HTTP response as shown in program 2.2. The "Sec-WebSocket-Accept" header is derived from the "Sec-WebSocket-Key" header from the client's handshake request. To get it, we combine the "Sec-WebSocket-Key" header and "258EAFA5-E914-47DA-95CA-C5AB0DC85B11" together. The second string is "a magic string". A magic string is predefined by the developer. It is made in a way where you would not expect it to be received from an input. When the "Sec-WebSocket-Key" header and the magic string are

combined, the SHA-1 hash is taken from the result, and the base64 encoding of the hash is returned [23]. The SHA-1 is a cryptographic hash function, while base64 is a binary-to-text encoding scheme.

WebSocket URIs. WebSocket defines two URI schemes. You can either use ws or the wss scheme. The ws (WebSocket) is a regular connection similar to http. While wss (web socket secure) is a secured connection similar to https. The schemes are built as follows:

```

ws-URI = "ws:" "//" host [ ":" port ] path [ "?" query ] wss-URI = "wss:" "//" host [ ":" port ] path [ "?" query ]

```

The most important components of the ws or wss are the host and its port. The host is determined by the server's IP address, while the port defines which port the server uses for the communication. If there is no specified port, the standard port used for ws is 80, and the standard port used for wss is 443.

**Data Frames.** The main advantage of WebSockets is bidirectional communication. So at any point in time, either the client or the server can send a message. Every data frame that is sent from the client to the server, or vice versa, follows the same format as seen in figure 2.8.

| 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5                                                         | 2<br>6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F R R R  opcode M  Payload len<br> I S S S  (4)  A  (7)<br> N V V V   S <br>  1 2 3   K | Extended payload length (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64) (16/64 |

|                                                                                         | Masking-key, if MASK set to 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Masking-key (continued)                                                                 | Payload Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Payload Date                                                                            | ta continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Payload Dat                                                                             | ta continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Figure 2.8 Standard WebSocket dataframe format

#### • FIN: 1 bit

Depending on the value of this bit, it either tells the receiving end whether or not this is the final fragment of the message. If the bit equals "0", it is not the last fragment and the receiver will continue listening for more fragments. If the bit equals "1", it means it is the last fragment of the message and the server will consider the message being delivered.

#### • RSV1, RSV2, RSV3: 1 bit each

All of these bits are reserved for WebSocket extensions. They should be "0" unless the client and server negotiated on whether or not a specific extension requires the use of any of the three bits. If any of these three bits is not zero while the client did not negotiate on any of these bits being non-zero, the receiving end will "fail" the WebSocket connection.

### • Opcode: 4 bits

These 4 bits will define how the receiving end should interprete the data. If the receiving end does not understand the opcode it will, as in the previous case, "fail" the WebSocket connection. The information about the different opcodes is found at [18].

x0: continuation frame; this frame contains data that should be appended to the previous frame

x2: binary frame; this frame (and any following) contains binary data

x3 - x7: non-control reserved frames; these are reserved for possible WebSocket extensions

x8: close frame; this frame should end the connection

x9: ping frame

xA: pong frame

xB - xF: control reserved frames

#### • Mask bit: 1 bit

This bit tells wether or not the frame uses a mask. If this bit is set to "1", a masking key is included in the message. This masking key is used to unmask the data in the payload. Every frame that is sent from the client to the server must have this bit set to "1".

#### • Payload length: 7 bits, 7+16 bits, 7+64bits

The seven bits determine the length of the payload. If these seven bits equal 126, or "1111110", the actual length is determined by bits 16 to 31 (so 16 extra bits). These are the following 2 bytes. If the seven bits equal 127, or "1111111", the actual length is determined by bits 16 to 79 (so 64 extra bits). These are the following 8 bytes.

#### • Masking key: 4 bytes

As mentioned previously, this field only exists if the mask bit is set to one. All the messages who have this field set to one, are masked by a 32-bit value. If the mask bit is set to zero, there will be no masking key in the first place.

#### • Payload data: x+y bytes

The payload data is the combination of the extension data and the application data. These two are listed below.

#### • Extension data: x bytes

The extension data is non-existent unless it was negotiated on the opening handshake between the server and the client. As mentioned earlier, the RSV1-3 bits are responsible for these extensions. Any extension that has been negotiated by the client and server must have a specified length of the "Extension data". It can also tell the receiving end on how to calculate this length. As said previously, the extension is part of the total payload data.

• Application data: y bytes

The application data contains the actual data that has be to transmitted. It takes up the remaining space in the frame after any extension data. The application data is, like the extension data, part of the payload data.

## 2.5 SoC

SoC is the abbreviation of System-on-Chip. In our case that is a processor, FPGA and peripherals together on a single substrate inside of one chip. Industry calls this process VLSI, Very Large Scale Integration. The main advantages of using VLSI in a SoC are the low power consumption, its tiny size and the fast well shielded connections between the on-chip components [12]. On the other hand, using VLSI makes the chip design, production and service very complicated. Due to the high components density, a lot of heat is concentrated at the same location. The only way to cool down the chip is by increasing package size. To minimise the package size SoCs only drive low power GPIOs. If there is a need for high power controls, a series of buffers must extend the GPIO, General Purpose Input Output, signals.

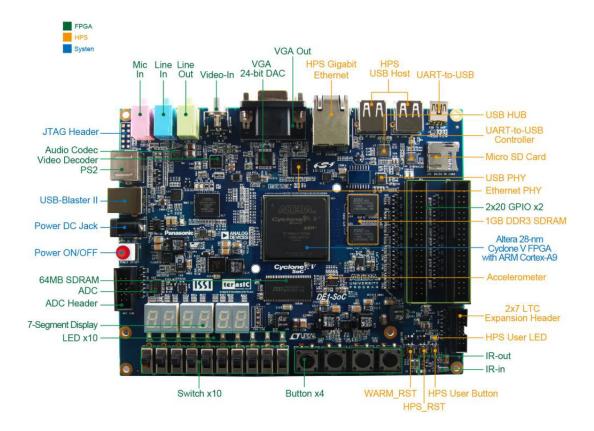

The SoC used in this thesis, Cyclone V 5CSEMA5FF31C6N [6] in figure 2.9, is made by Altera and integrated in the DE1SoC development board by TerASIC [30]. The DE1SoC consist of a HPS- and a FPGA-part with both their own peripherals. HPS is the abbreviation of Hard Processing System and FPGA for Field Programmable Gate Array. Figure 2.9 shows most of those components and the system they are connected to. Orange peripherals are connected with the HPS, while green components are peripherals of the FPGA and everything in blue is commonly used. Inside the Cyclone V IC, three bridges are provided to distribute signals between FPGA and HPS. Because all the GPIO's are connected to the FPGA, all GPIO data are always transferred through the bridges, when they are needed by the HPS. The FPGA-part can be configured by a HDL, Hardware Description Language [13]. In contrary to regular programming languages, HDL describes digital hardware. Instead of programming a single thread and running each command at a time a FPGA implements parallel applications, resulting in a high throughput. HDL describes a full data path of registers, adders, multiplexers, etc. between multiple PLLs (Phase-Locked Loop), FSM (Finite State Machine) controllers and other modules.

Figure 2.9 Layout of the DE1SoC development board of TerASIC

In the following sections we will discuss why a HPS, FPGA and bridges between the two are necessary.

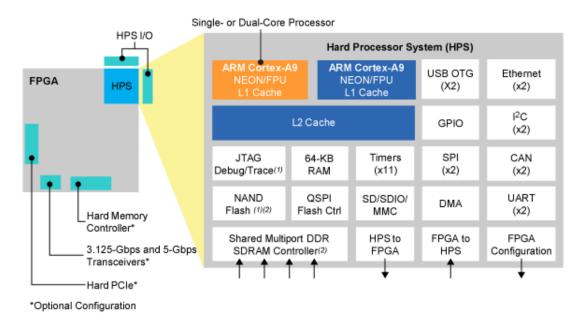

# 2.5.1 Hard Processing System

Embedding one or more processors inside electronic systems gives the advantages of faster development time and in-the-field reprogrammability. The SoC we use includes a HPS with two ARM Cortex A9 cores, as can be seen in figure 2.10. Each processor uses its own L1 cache memory capable of storing 64 KB, of which 32KB is reserved for instructions and 32KB for data. L1 cache is relatively small, but provides a high speed read and write memory to the processor [22]. Dual-core applications need a shared cache memory when they exchange data between two processors. Shared cache memory is called L2 cache and is larger, but slower than L1 cache. DDR SDRAM is provided in the HPS, so the OS can boot. Developers can use the "Shared multiport DDR SDRAM controller" to read and write SDRAM data from the FPGA. There are three more connections, called bridges, in the SoC: "HPS to FPGA", "FPGA to HPS" and "FPGA Configuration". The third bridge gives developers the ability to upload a raw binary file to configure the FPGA from HPS. During runtime the "HPS to FPGA" and "FPGA to HPS" bridges can be called to exchange data. Other HPS peripherals are shown in

Figure 2.10 Cyclone V Hard Processing System layout

figure 2.10. We will not discuss them because the OS deals with them in the background.

Our SoC consists of a 32-bit, 800MHz dual-core ARM Cortex A9 MPCore architecture [5]. The data path size and width of the registers are both 32 bits. The term dual-core refers to two independent processing units with the ARM Cortex A9 MPCore architecture in the same package, running at a frequency of 800MHz. This architecture is highly recommended for low-power, cost-effective applications on a 32-bit platform.

In the next paragraphs we will explain why we need an Operating System and programming languages such as C++ and OpenCL and how we use them. The HPS has a processing unit and lots of peripherals, software is needed to use all of them in a structured way. This software is built on an interface that is called an Operating System. Operating systems are built with programming languages to execute programming languages. Embedded systems are mostly built of C or C++ source code. Besides C and C++ executables running on the HPS, we used OpenCL to program the FPGA with a kernel.

#### Operating system

As defined in "Research paper on operating system" [9]: "An OS is a collection of software that manages computer hardware resources and provides common services for computer programs. The operating system is an essential component of the system software in a computer. Application programs usually require an operating system to function".

The used OS on the DE1SoC board is provided by Altera and is a basic Linux kernel without

user interface. Because the kernel does only support command line, the impact of running an OS on the CPU is minimised. This kernel already has all the packages we need to run OpenCL, C++ and use the AMBA AXI bridges. More info about OpenCL can be found in paragraph 2.2.3. Altera has chosen the Angstrom Linux distribution for their SoC [7]. Angstrom is a very basic Linux distribution used in a variety of embedded devices. The popularity of embedded systems is due to the fact that it uses a binary package feed, allowing to simply install software distributed as OPKG packages. Those OPKG packages are precompiled on a host system.

#### Programming language

A programming language is defined as the communicator of instructions to the computer. Depending on the language used a certain knowledge of the architecture is needed. When programming in machine language for example, processor architecture must be well known. Each architecture has its own instruction set, with one instruction for each operation. All instructions correspond one on one to a physical command in the machines processor architecture. A command can be anything like loading data into registers or calculating a result from two data registers. Machine language is the most basic programming language. Programmers should have adequate experience with the specific architecture to program simple applications in an efficient way. Nowadays, with the wide variety of systems and architectures, programs are written in a higher level programming language. Those languages, such as C, C++, Java or C#, are easier to develop and distribute over different platforms. Higher level programming languages are still based on the same machine language for their specific architecture, but a compiler handles the conversion to machine language instead of the developer. The compiler generates an executable in different stages by using a preprocessor, compiler, assembler and linker.

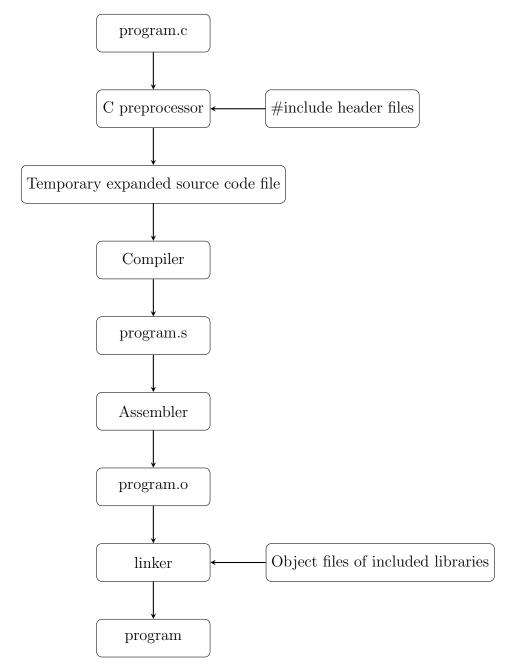

The compilation process of a C++ program can be found in figure 2.11 [20]. A preprocessor copies the source code file and includes header files into a temporary expanded source code file. During the copying process all "#defines" are initialised with their values. Next, the temporary expanded source code file is translated to assembly language. This code is based on the desired architecture, resulting in a specific assembly code for each architecture. Assembly code passing through the assembler generates an object file. While the object file is generated, physical memory locations will be assigned to all variables and instructions are given by the assembly code. During the last step the previously generated object file is linked with other object files corresponding to the earlier included header files. By linking object files, one executable file is generated. Executables are started when the "./program" command is invoked. Executables can only be started when the user has given execution rights to the specific executable file. Users give the execution rights by the "chmod +x" command, used as "chmod +x executableFileName".

Figure 2.11 Compilation process from High level programming language to an executable file [17]