## Capacitance-voltage characterization of GaAs – $Al_2O_3$ interfaces

Cite as: Appl. Phys. Lett. **93**, 183504 (2008); https://doi.org/10.1063/1.3005172 Submitted: 01 September 2008 . Accepted: 15 September 2008 . Published Online: 03 November 2008

G. Brammertz, H.-C. Lin, K. Martens, D. Mercier, S. Sioncke, A. Delabie, W. E. Wang, M. Caymax, M. Meuris, and M. Heyns

## **ARTICLES YOU MAY BE INTERESTED IN**

Characteristic trapping lifetime and capacitance-voltage measurements of GaAs metaloxide-semiconductor structures Applied Physics Letters **91**, 133510 (2007); https://doi.org/10.1063/1.2790787

Comparison of methods to quantify interface trap densities at dielectric/III-V semiconductor interfaces Journal of Applied Physics **108**, 124101 (2010); https://doi.org/10.1063/1.3520431

Temperature and frequency dependent electrical characterization of  $HfO_2/In_xGa_{1-x}As$  interfaces using capacitance-voltage and conductance methods Applied Physics Letters **94**, 102902 (2009); https://doi.org/10.1063/1.3089688

Appl. Phys. Lett. **93**, 183504 (2008); https://doi.org/10.1063/1.3005172 © 2008 American Institute of Physics.

## Capacitance-voltage characterization of GaAs-Al<sub>2</sub>O<sub>3</sub> interfaces

G. Brammertz,<sup>a)</sup> H.-C. Lin, K. Martens, D. Mercier, S. Sioncke, A. Delabie, W. E. Wang, M. Caymax, M. Meuris, and M. Heyns

Interuniversity Microelectronics Center (IMEC vzw), Kapeldreef 75, B-3001 Leuven, Belgium

(Received 1 September 2008; accepted 15 September 2008; published online 3 November 2008)

The authors apply the conductance method at 25 and 150 °C to GaAs-Al<sub>2</sub>O<sub>3</sub> metal-oxide-semiconductor devices in order to derive the interface state distribution  $(D_{it})$  as a function of energy in the bandgap. The  $D_{it}$  is governed by two large interface state peaks at midgap energies, in agreement with the unified defect model. S-passivation and forming gas annealing reduce the  $D_{it}$  in large parts of the bandgap, mainly close to the valence band, reducing noticeably the room temperature frequency dispersion. However the midgap interface state peaks are not affected by these treatments, such that Fermi level pinning at midgap energies remains. © 2008 American Institute of Physics. [DOI: 10.1063/1.3005172]

We have recently shown that due to the larger bandgap of GaAs as compared to Si, the midgap interface states in GaAs are too slow to respond to the usual CV-characterization frequencies at room temperature.<sup>1</sup> In addition to room temperature measurements, measurements at higher substrate temperatures are also needed in order to deduce the characteristics of the interface states over the whole bandgap and in particular at midgap energies. In the following, we will apply the conductance method<sup>2</sup> to alternating current (ac) CV measurements performed with substrate temperatures of 25 and 150 °C on both *n*- and *p*-type GaAs substrates, in order to deduce the  $D_{it}$  as a function of energy in the whole bandgap. Alternative methods to derive the interface state density over the whole bandgap are quasistatic CV measurements with very slow sweep rates and long integration times<sup>3</sup> or photoluminescence intensity measurements.<sup>3</sup>

The samples analyzed in this work consist of 5  $\times 10^{17}$  cm<sup>-3</sup> Si- (*n*-type) or Zn- (*p*-type) doped GaAs substrates on which 10 nm Al<sub>2</sub>O<sub>3</sub> was grown by atomic layer deposition (ALD) in an ASM Pulsar ALD reactor. The Al<sub>2</sub>O<sub>3</sub> was deposited at 300 °C using alternating pulses of H<sub>2</sub>O and trimethylaluminum. Prior to deposition, two different surface treatments were applied. A first set of samples (n- and *p*-type) received a 5 min HCl clean and a second set of samples (*n*- and *p*-type) received a 5 min  $(NH_4)_2S$  wet chemical clean. The resulting four samples got an Ohmic contact on the back side consisting of AuZn/Au (p-type) or AuGe/Ni/Au (n-type) multilayers, followed by a 30 s 380 °C forming gas anneal (FGA). On the front side Pt metal dots were deposited through a shadow mask. In addition, the samples with the  $(NH_4)_2S$  clean were further treated with a 30 min FGA at 400 °C. 200  $\mu$ m diameter metal dot capacitors were then measured with a standard HP 4284 LCR meter. In order to get a continuous picture of the  $D_{it}$ , 25 frequencies were measured varying logarithmically from 100 Hz to 1 MHz.

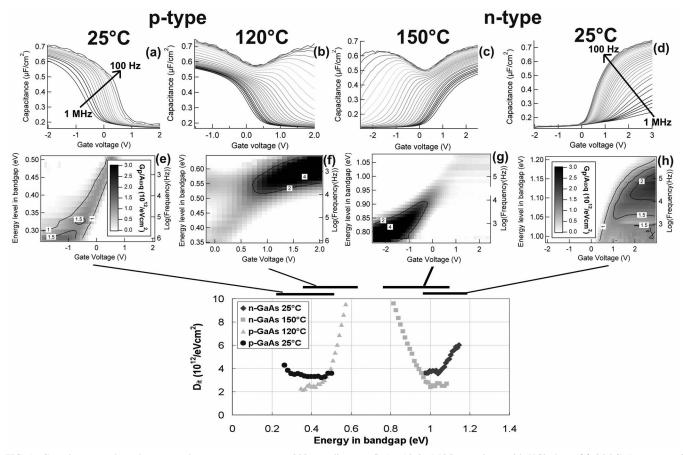

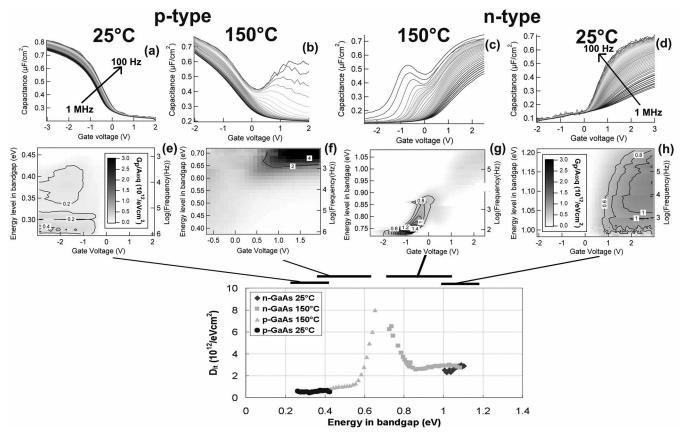

The experimental results from the samples with HCl clean are shown in Fig. 1, whereas the data for the S-treated samples with FGA is shown in Fig. 2. The four figures on the upper line show the regular CV data for the 25 measured frequencies of the *n*- and *p*-type samples at 25 and 150 °C,

respectively. The four figures on the lower line represent the conductance data, plotted as a conductance map, which shows a two dimensional contour plot of the normalized substrate conductance  $(G_{p/}A\omega q)$  as a function of bias voltage and measurement frequency. Here,  $G_p$  is the substrate conductance, derived from the measured conductance  $G_m$  by correcting for the oxide capacitance  $(C_{\text{ox}})$ ,<sup>2</sup> $\omega$  is the measurement pulsation, and q is the majority carrier charge. In the conductance plots of Figs. 1 and 2, the measurement frequency f on the vertical axis was directly transformed into trap energy in the bandgap  $E_t$ , using the characteristic emission time constants of the interface states, which behave according to general Fermi–Dirac statistics,<sup>4</sup>

$$\tau = \frac{1}{\sigma v_t N} \exp(\Delta E/kT), \tag{1}$$

where  $\Delta E$  is the energy difference between the majority carrier band edge energy and the trapping state energy  $E_t$  (depth of the trap), k is the Boltzmann constant, T is the semiconductor temperature,  $\sigma$  is the capture cross section of the trapping state,  $v_t$  is the thermal velocity of the majority charge carriers, and N is the density of states in the majority carrier band. From this characteristic emission time  $\tau$ , one can directly derive the characteristic response frequency f =1/2 $\pi\tau$  of a trapping state, knowing the depth of the trapping state in the bandgap. This equation shows that the characteristic emission frequency depends exponentially on the depth of the trapping state in the bandgap. The further the trap is away from the band edge, the slower it will emit a trapped charge. More details can be found in Ref. 1. Concerning the parameter values from Eq. (1), the thermal velocity and density of states are well known and well defined values for a specific semiconductor,<sup>5</sup> whereas the trap capture cross section depends strongly on the nature of the trap.<sup>6</sup> The capture cross section can take values varying from  $10^{-12}$  to  $10^{-20}$  cm<sup>2</sup>. Even larger values than  $10^{-12}$  cm<sup>2</sup> cannot be excluded. Nevertheless, the largest majority of trapping states has capture cross sections of the order of  $10^{-15}$  cm<sup>2</sup> (Ref. 6). In the following, a capture cross section of  $10^{-15}$  cm<sup>2</sup> is assumed in order to illustrate the effects of the characteristic emission time constant. Assuming a value for the capture cross section leads of course to an uncertainty concerning the absolute position of the interface state position in the bandgap. The further the real trap capture cross

<sup>&</sup>lt;sup>a)</sup>Electronic mail: guy.brammertz@imec.be.

FIG. 1. Capacitance- and conductance-voltage measurements on 200  $\mu$ m diameter GaAs/Al<sub>2</sub>O<sub>3</sub> MOS capacitors with HCl clean: (a) 25 °C CV curves of *p*-type GaAs capacitor, (b) 120 °C CV curves of *p*-type GaAs capacitor, (c) 150 °C CV curves of *n*-type GaAs capacitor, (d) 25 °C CV curves of *n*-type GaAs capacitor, (e) 25 °C G<sub>p</sub>/A  $\omega$ q map of *p*-type GaAs capacitor, (f) 120 °C G<sub>p</sub>/A  $\omega$ q map of *p*-type GaAs capacitor, (g) 150 °C G<sub>p</sub>/A  $\omega$ q map of *n*-type GaAs capacitor, (g) 150 °C G<sub>p</sub>/A  $\omega$ q map of *n*-type GaAs capacitor, (h) 25 °C G<sub>p</sub>/A  $\omega$ q map of *n*-type GaAs capacitor. The lower graph shows the GaAs–Al<sub>2</sub>O<sub>3</sub> (HCl clean) D<sub>it</sub> derived from the four conductance maps, the arrows indicating which measurement measures the interface state density in what portion of the bandgap.

section is off with respect to our assumed value of  $10^{-15}$  cm<sup>-2</sup>, the larger the error. Nevertheless, the exponential term in Eq. (1) is dominant and simple arithmetic on Eq. (1) shows that even a variation of the capture cross section by three orders of magnitude will only give rise to an energy difference of 0.18 eV. This somewhat exotic method of positioning the interface states in the bandgap is necessary because usually the conductance method relies on the determination of the flatband voltage in order to position the interface states in the bandgap, whereas this value can not be determined for our heavily pinned devices.<sup>7</sup>

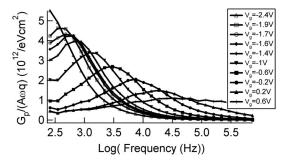

In order to clarify the data in the conductance maps, Fig. 3 shows a subset of the data of Fig. 1(g) in a more generally accepted way of representing conductance data. This will allow the reader to interpret the data in the conductance maps. Nevertheless, the conductance maps show the conductance data in a more efficient and intuitive way, as it allows visualizing the movement of the surface Fermi level as the gate bias is varied. Clearly, the frequency for which the maximum in the conductance data for every gate bias occurs corresponds to the characteristic frequency of the trapping states at the energy position in the vicinity of the surface Fermi level position at that precise gate bias. Therefore, following the maxima in the conductance map visualizes how the surface Fermi level moves over the energy gap as the gate bias is varied. When this trace of maximum conductance turns horizontal, as can be seen in particular on Figs. 1(f), 1(g), 2(f), and 2(g), the Fermi level is effectively hindered

from moving, which is generally expressed by the term Fermi level pinning. This can be easily visualized in such a conductance map. Applying the conductance method,<sup>2</sup> i.e., extracting the interface state data from the height of the conductance peaks, the  $D_{it}$  shown in the lower parts of Figs. 1 and 2 can be derived. Note that in the region where  $G_p/\omega$ approaches  $C_{\text{ox}}$  ( $D_{\text{it}} > 10^{13}$ /eV cm<sup>2</sup>), the extracted values are lower limits to the real  $D_{\text{it}}$ .<sup>7</sup> We can see that for both the HCl-cleaned and the S-cleaned samples, the  $D_{it}$  is governed by two large peaks around midgap energies. This is in agreement with the unified defect model<sup>8</sup> (UDM) and the pinned Fermi level around midgap energies for the vast majority of GaAs interfaces,<sup>9</sup> with the exception of the Ga<sub>2</sub>O<sub>3</sub> passivated interface.<sup>10</sup> In addition, we see that somewhat closer to the conduction band, there is another much smaller peak. Photoluminescence spectroscopy data of Si-doped samples (not shown here) as well as deep level transient spectroscopy measurements<sup>11</sup> indicate that this smaller peak seems to be related to a Si defect in the bulk of the GaAs layer. This is also confirmed by the shape of the conductance peaks in Figs. 1(h) and 2(h), which have a more plateaulike shape toward accumulation, without a clear maximum, which is a typical signature of bulk defects.<sup>2</sup> The effect of the S-passivation and FGA can also be clearly seen. It reduces the  $D_{it}$  close to the valence band to levels close to mid- $10^{11}$ /cm<sup>2</sup> eV. As a consequence of this reduction, the frequency dispersion in the room temperature CV curves of

FIG. 2. Capacitance- and conductance-voltage measurements on 200  $\mu$ m diameter GaAs/Al<sub>2</sub>O<sub>3</sub> MOS capacitors with S-passivation and FGA: (a) 25 °C *CV* curves of *p*-type GaAs capacitor, (b) 150 °C *CV* curves of *p*-type GaAs capacitor, (c) 150 °C *CV* curves of *n*-type GaAs capacitor, (d) 25 °C *CV* curves of *n*-type GaAs capacitor, (e) 25 °C *G<sub>p</sub>*/A $\omega$ *q* map of *p*-type GaAs capacitor, (f) 120 °C *G<sub>p</sub>*/A $\omega$ *q* map of *p*-type GaAs capacitor, (g) 150 °C *CV* curves of *n*-type GaAs capacitor, (h) 25 °C *G<sub>p</sub>*/A $\omega$ *q* map of *n*-type GaAs capacitor. The lower graph shows the GaAs–Al<sub>2</sub>O<sub>3</sub> (S-passivated) *D*<sub>it</sub> derived from the four conductance maps, the arrows indicating which measurement measures the interface state density in what portion of the bandgap.

the *p*-type samples is strongly reduced [Fig. 2(a)]. The region close to the conduction band does not seem to be affected as much by the S-passivation and FGA [Figs. 1(d) and 2(d)]. Most importantly, the two large midgap peaks, which completely dominate the  $D_{it}$ , although somewhat reduced or shifted in energy position, do not disappear. The Fermi level is still pinned around midgap energies. ALD Al<sub>2</sub>O<sub>3</sub> with S-passivation and FGA is therefore not able to passivate the GaAs interface. Fermi level pinning around midgap energies for both *n*- and *p*-type GaAs remains, similar to molecular beam epitaxy deposited Al<sub>2</sub>O<sub>3</sub> on GaAs.<sup>10</sup>

We have shown how the conductance method can be applied at 25 and 150 °C in order to derive the  $D_{\rm it}$  over the whole bandgap of GaAs. Experimental measurements on HCl- and S-cleaned GaAs-Al<sub>2</sub>O<sub>3</sub> metal-oxide-

FIG. 3. More common representation of a subset of the conductance data from Fig. 1(g):  $G_p/A\omega q$  as a function of frequency for different gate bias voltages.

semiconductor (MOS) capacitors show that two large peaks around midgap energies govern the properties of the GaAs surface, which is in agreement with the UDM by Spicer *et al.* Although S-passivation and FGA have some beneficial effects on the interface state density, reducing notably the room temperature frequency dispersion of p-type devices, Fermi level pinning around midgap energies is still present.

The authors acknowledge support by the European Commission's project FP7-ICT-DUALLOGIC No. 214579 *Dualchannel CMOS for (sub)*-22 nm *high performance logic*.

- <sup>1</sup>G. Brammertz, K. Martens, S. Sioncke, A. Delabie, M. Caymax, M. Meuris, and M. Heyns, Appl. Phys. Lett. **91**, 133510 (2007).

- <sup>2</sup>E. H. Nicollian and J. R. Brews, *MOS (Metal Oxide Semiconductor) Physics and Technology* (Wiley, New York, 1981), p. 286.

- <sup>3</sup>M. Passlack, *Materials Fundamentals of Gate Dielectrics* (Springer, Dordrecht, The Netherlands, 2005), p. 403.

- <sup>4</sup>W. Shockley and W. T. Read, Phys. Rev. 87, 835 (1953).

- <sup>5</sup>See: http://www.ioffe.rssi.ru/SVA/NSM/

- <sup>6</sup>N. P. Khuchua, L. V. Khvedelidze, M. G. Tigishvili, N. B. Gorev, E. N. Privalov, and I. F. Kodzhespirova, Mikroelektronika **32**, 257 (2003).

- <sup>7</sup>K. Martens, C. O. Chui, G. Brammertz, B. De Jaeger, D. Kuzum, M. Meuris, M. M. Heyns, T. Krishnamohan, K. Saraswat, H. E. Maes, and G. Groeseneken, IEEE Trans. Electron Devices 55, 547 (2008).

- <sup>8</sup>W. E. Spicer, I. Lindau, P. Skeath, and C. Y. Su, J. Vac. Sci. Technol. **17**, 1019 (1980).

- <sup>9</sup>H. Lüth, *Solid Surfaces, Interfaces and Thin Films*, 4th ed. (Springer, Berlin, 2001), p. 343.

- <sup>10</sup>M. Passlack, M. Hong, J. P. Mannaerts, J. R. Kwo, and L. W. Tu, Appl. Phys. Lett. **68**, 3605 (1996).

- <sup>11</sup>B. J. Skromme, S. S. Bose, B. Lee, T. S. Low, T. R. Lepkowski, R. Y. DeJule, G. E. Stillman, and J. C. M. Hwang, J. Appl. Phys. **58**, 4685 (1985).