# Faculteit Industriële Ingenieurswetenschappen

master in de industriële wetenschappen: elektronica-ICT

#### **Masterthesis**

Designing an amplifier for biomedical signals in IGZO

#### Mauro Vranckx

Scriptie ingediend tot het behalen van de graad van master in de industriële wetenschappen: elektronica-ICT

#### **PROMOTOR:**

Prof. dr. ing. Kris MYNY

#### **PROMOTOR:**

ir. Mohit DANDEKAR

Gezamenlijke opleiding UHasselt en KU Leuven

**KU LEUVEN**

Universiteit Hasselt | Campus Diepenbeek | Faculteit Industriële Ingenieurswetenschappen | Agoralaan Gebouw H - Gebouw B | BE 3590 Diepenbeek

Universiteit Hasselt | Campus Diepenbeek | Agoralaan Gebouw D | BE 3590 Diepenbeek Universiteit Hasselt | Campus Hasselt | Martelarenlaan 42 | BE 3500 Hasselt

$\frac{2024}{2025}$

# Faculteit Industriële Ingenieurswetenschappen

master in de industriële wetenschappen: elektronica-ICT

#### **Masterthesis**

Designing an amplifier for biomedical signals in IGZO

#### **Mauro Vranckx**

Scriptie ingediend tot het behalen van de graad van master in de industriële wetenschappen: elektronica-ICT

#### **PROMOTOR:**

Prof. dr. ing. Kris MYNY

#### **PROMOTOR:**

ir. Mohit DANDEKAR

## **Preface**

I would like to begin this master's thesis by expressing my heartfelt appreciation to my supervisors, prof. dr. ing. Kris Myny, ing. Yari Nowicki and ir. Muhammed Dawood Asghar, whose unwavering support and guidance helped me through this journey and encouraged me to push further to reach the conclusion presented in this thesis. Thank you for all your feedback, and most importantly, your time.

Second, I would like to thank my girlfriend, who helped me understand various biological topics and supported me with patience and unwavering encouragement. I am also grateful to my parents and brother, who, despite not having much insight into the subject, were always eager to hear about the latest developments and remained supportive throughout the process. Lastly, I want to thank the students who worked alongside me during this time. Their dedication and sense of healthy competition pushed me to achieve more.

#### Thank you all.

With this thesis, a new chapter in life begins. I hope this thesis will encourage and inspire you, and others, to delve deeper into the field of analogue circuits for flexible electronics, as it holds broad and meaningful potential for real-world applications in everyday life.

# Contents

| $\mathbf{P}$              | refac  | e                                                 | ]       |

|---------------------------|--------|---------------------------------------------------|---------|

| $\mathbf{L}^{\mathrm{i}}$ | ist of | Tables                                            | 7       |

| $\mathbf{L}^{\mathrm{i}}$ | ist of | Figures                                           | 10      |

| $\mathbf{A}$              | crony  | ym List                                           | 11      |

| $\mathbf{A}$              | bstra  | nct                                               | 13      |

| $\mathbf{A}$              | bstra  | act in Dutch                                      | 15      |

| 1                         | Inti   | roduction                                         | 17      |

|                           | 1.1    | Motivation                                        | 1'      |

|                           |        | 1.1.1 Emerging Technologies, Systems and Security |         |

|                           | 1.2    | Problem Statement                                 |         |

|                           | 1.2    | 1.2.1 Electrocardiogram Signals                   |         |

|                           |        | 1.2.2 Noise Sources                               |         |

|                           |        | 1.2.3 Material Constraints                        |         |

|                           | 1.3    | Objectives                                        |         |

|                           | 1.4    | Method                                            |         |

|                           | 1.1    | 1.4.1 Differential Stage                          |         |

|                           |        | 1.4.2 Amplification Stage                         |         |

|                           |        | 1.4.3 Chopping                                    |         |

|                           | 1.5    | Thesis Outline                                    |         |

|                           | 1.0    | Thesis Outline                                    | ۷.      |

| 2                         | Lite   | erature Study                                     | 23      |

|                           | 2.1    | Introduction                                      | 23      |

|                           | 2.2    | Thin-Film Transistor Technologies                 | 23      |

|                           |        | 2.2.1 Low-Temperature Polycrystalline Silicon     | 23      |

|                           |        | 2.2.2 Amorphous Silicone                          | 23      |

|                           |        | 2.2.3 Amorphous Indium Gallium Zinc Oxide         | $2^{2}$ |

|                           | 2.3    | Amplifiers                                        | $2^{2}$ |

|                           |        | 2.3.1 Single-Stage Amplifier                      | $2^{2}$ |

|                           |        | 2.3.2 Differential Amplifier                      |         |

|                           |        | 2.3.3 Current Mirror                              | 2       |

|                           | 2.4    | Improving Gain                                    | 20      |

|    |       | 2.4.1 Bootstrapping                                                                                            |    |

|----|-------|----------------------------------------------------------------------------------------------------------------|----|

|    |       | 2.4.2 Cascoding                                                                                                |    |

|    | 2.5   | Chopping                                                                                                       | 32 |

|    | 2.6   | Feedback                                                                                                       | 33 |

|    | 2.7   | Bio-Potential Amplifiers                                                                                       | 34 |

|    |       | 2.7.1 CMOS                                                                                                     | 34 |

|    |       | 2.7.2 Unipolar MOS                                                                                             | 35 |

|    | 2.8   | Analogue Front-End                                                                                             | 37 |

|    | 2.9   | Conclusion                                                                                                     | 37 |

| 3  | Des   | igned Circuits                                                                                                 | 39 |

|    | 3.1   | Introduction                                                                                                   | 39 |

|    | 3.2   | Simple Differential Amplifier                                                                                  | 39 |

|    | 3.3   | Diode-Load Differential Amplifier                                                                              | 41 |

|    | 3.4   | Bootstrapped Differential Amplifier                                                                            | 42 |

|    | 3.5   | Transconductance Boosting Differential Amplifier                                                               |    |

|    | 3.6   | Implemented Feedback                                                                                           | 45 |

|    | 3.7   | Chopping Modulation Circuit                                                                                    | 45 |

| 4  | Sim   | ulations and Analysis                                                                                          | 47 |

|    | 4.1   | Designed Test Benches                                                                                          | 47 |

|    |       | 4.1.1 Frequency Response                                                                                       | 47 |

|    |       | 4.1.2 Transient Response                                                                                       | 48 |

|    |       | 4.1.3 Common-Mode Rejection Ratio                                                                              | 48 |

|    | 4.2   | Differential Amplifier Simulation Results                                                                      | 49 |

|    |       | 4.2.1 Simple Differential Amplifier                                                                            | 49 |

|    |       | 4.2.2 Diode-Load Differential Amplifier                                                                        | 51 |

|    |       | 4.2.3 Bootstrapped Differential Amplifier                                                                      | 53 |

|    |       | 4.2.4 Transconductance Boosting Differential Amplifier                                                         | 55 |

|    | 4.3   | Electrocardiogram Test Bench                                                                                   | 57 |

|    | 4.4   | Electrocardiogram Simulation Results                                                                           | 58 |

|    |       | 4.4.1 Simple Differential Amplifier                                                                            | 59 |

|    |       | 4.4.2 Transconductance Boosting Differential Amplifier                                                         | 61 |

|    | 4.5   | Conclusion                                                                                                     | 63 |

| 5  | Con   | aclusion and Discussion                                                                                        | 65 |

|    | 5.1   | Conclusion                                                                                                     | 65 |

|    | 5.2   | Limitations of the Differential Amplifier and Potential Improvements                                           | 66 |

|    | 5.3   | Limitations of the Study and Future Work                                                                       | 66 |

| Ac | knov  | wledgment                                                                                                      | 67 |

| Bi | bliog | graphy                                                                                                         | 74 |

|    |       | pendix - Layout Images                                                                                         | 75 |

|    |       | , and the second se |    |

| В  | App   | pendix - Calculations                                                                                          | 81 |

| $\mathbf{C}$ | Appendix - Bode Plot CMRR                   | 91 |

|--------------|---------------------------------------------|----|

| D            | Appendix - No Miller Compensation Bode Plot | 93 |

| $\mathbf{E}$ | Appendix - Electrocardiogram Recordings     | 95 |

# List of Tables

| 3.1 | $g_m/I_d$ Design Trade-offs                                      | 39         |

|-----|------------------------------------------------------------------|------------|

| 3.2 | Simple Differential Amplifier Sizes and Values                   | 40         |

| 3.3 | Diode-Load Differential Amplifier Sizes and Values               | 41         |

| 3.4 | Bootstrapped Differential Amplifier Sizes and Values             | 43         |

| 3.5 | Transconductance Boost Differential Amplifier Sizes and Values   | 44         |

| 3.6 | Chopping Modulation Circuit Sizing                               | 46         |

| 4 1 |                                                                  | <b>-</b> 0 |

| 4.1 | Simple Differential Amplifier Obtained Values                    | 50         |

| 4.2 | Diode-Load Differential Amplifier Obtained Values                | 52         |

| 4.3 | Bootstrapped Differential Amplifier Obtained Values              | 55         |

| 4.4 | Transconductance Boosting Differential Amplifier Obtained Values | 57         |

| 4.5 | Comparison with State-of-the-Art Designs                         | 64         |

# List of Figures

| 1.1  | Visual Representation of an ECG Signal                                      | 18 |

|------|-----------------------------------------------------------------------------|----|

| 1.2  | White and $1/f$ Noise In Function of Frequency                              | 18 |

| 2.1  | Common-Source Amplifier                                                     | 24 |

| 2.2  | Diode-Connected Load                                                        | 25 |

| 2.3  | Differential Amplifier Circuit                                              | 26 |

| 2.4  | Current Mirror Circuit                                                      | 28 |

| 2.5  | Cascoding Current Mirror                                                    | 28 |

| 2.6  | Bootstrapping Circuit                                                       | 30 |

| 2.7  | Cascoding Amplifier                                                         | 31 |

| 2.8  | Chopping Modulation                                                         | 32 |

| 2.9  | Negative Feedback System                                                    | 33 |

| 2.10 | CMOS ECG Amplifier                                                          | 34 |

| 2.11 | NMOS Only OPAMP Design                                                      | 35 |

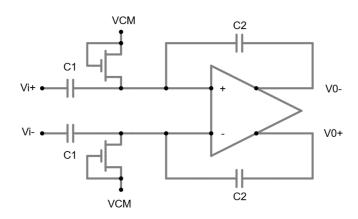

| 2.12 | Fully Differential OPAMP with Input Chopping                                | 36 |

| 2.13 | Visual Representation of an Analogue Front-End                              | 37 |

| 3.1  | Three Stage Simple Differential Amplifier                                   | 40 |

| 3.2  | Three Stage Diode-Load Differential Amplifier                               | 41 |

| 3.3  | Diode-Load Differential Amplifier Layout                                    | 42 |

| 3.4  | Two Stage Bootstrapped Differential Amplifier                               | 43 |

| 3.5  | Two Stage Transconductance Boosting Differential Amplifier                  | 44 |

| 3.6  | Capacitive Feedback on Differential Amplifier                               | 45 |

| 3.7  | Chopping Modulator                                                          | 45 |

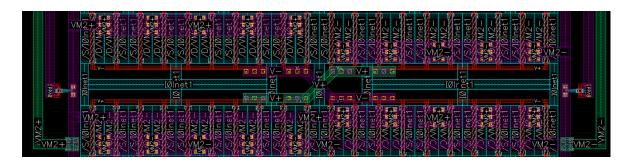

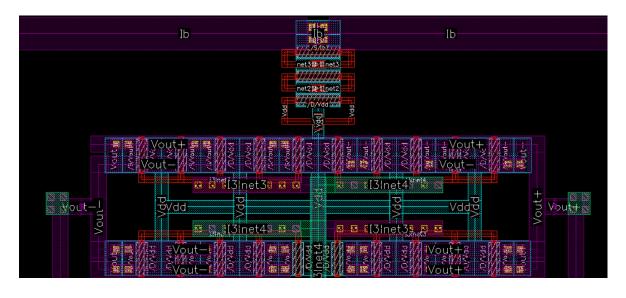

| 3.8  | Chopping Modulator Layout                                                   | 46 |

| 4.1  | Frequency Response Test Bench                                               | 47 |

| 4.2  | Square Wave Transient Response Test Bench                                   | 48 |

| 4.3  | Common-Mode Test Bench                                                      | 48 |

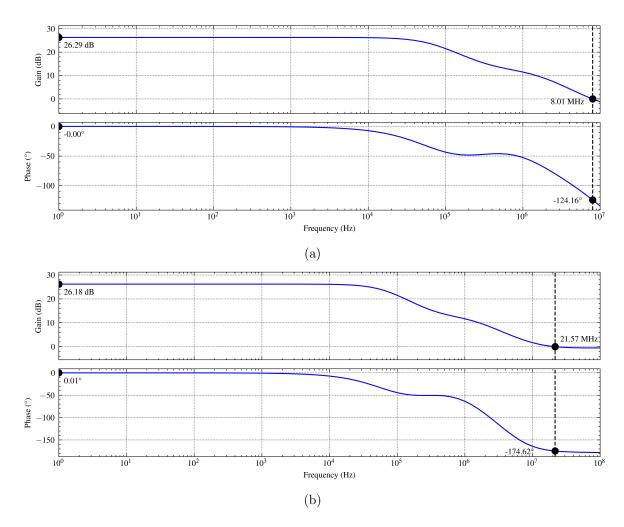

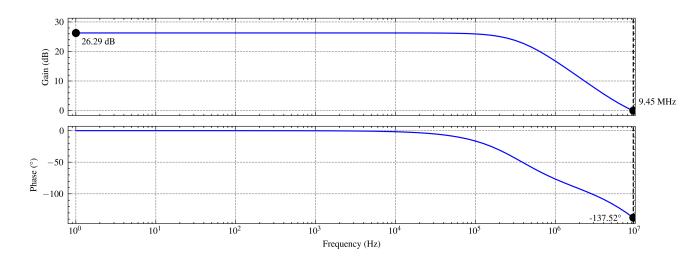

| 4.4  | Bode Plot Simple Differential Amplifier With and Without Feedback           | 49 |

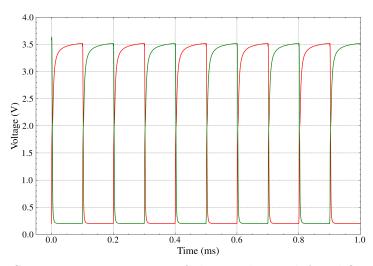

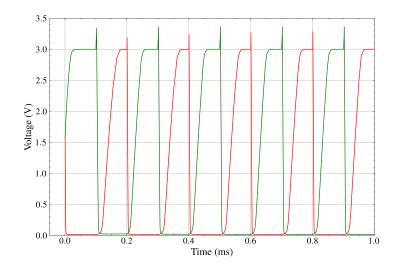

| 4.5  | Square Wave Response of the Simple Differential Amplifier Closed-Loop       | 50 |

| 4.6  | Bode Plot Diode-Load Differential Amplifier With and Without Feedback       | 51 |

| 4.7  | Square Wave Response of the Diode-Load Amplifier Open-Loop                  | 52 |

| 4.8  | Bode Plot Bootstrapped Differential Amplifier With and Without Feedback     | 53 |

| 4.9  | Square Wave Response of the Bootstrapped Differential Amplifier Open-Loop   | 54 |

| 4.10 | Square Wave Response of the Bootstrapped Differential Amplifier Closed-Loop | 54 |

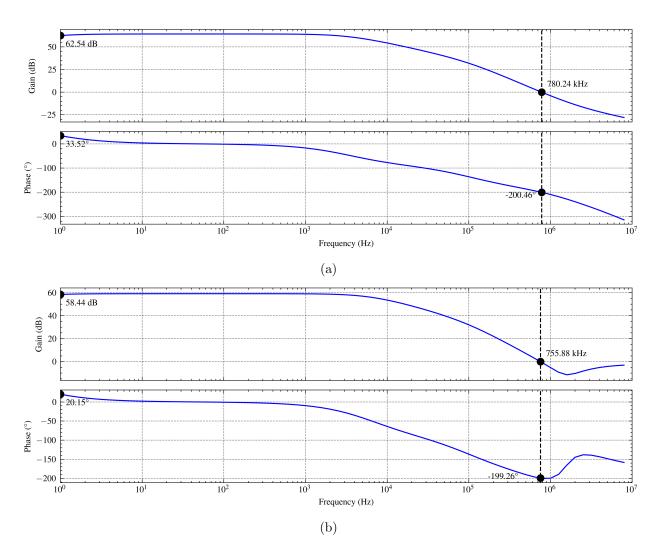

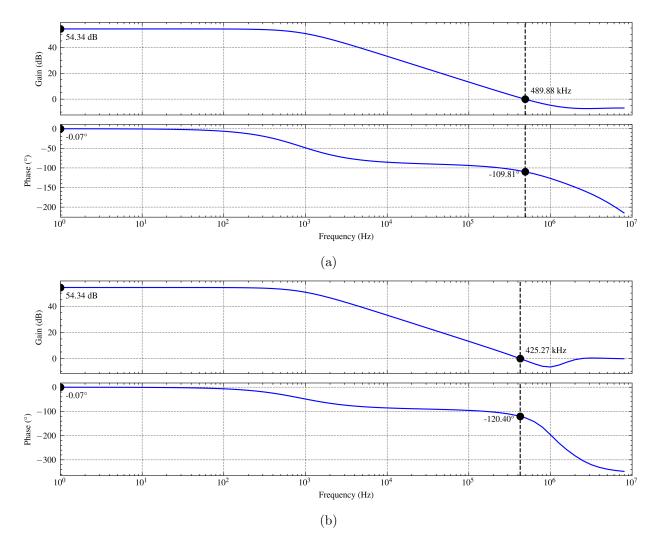

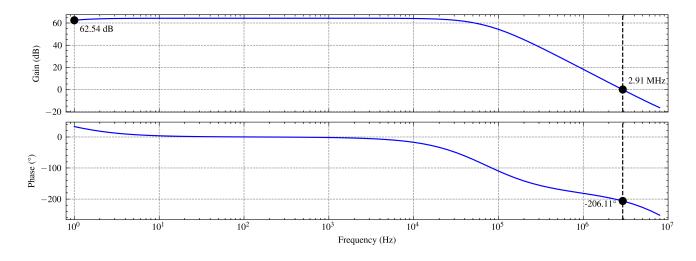

| 4.11 | Bode Plot Transconductance Boosting Differential Amplifier With and Without Feedback     | 55 |

|------|------------------------------------------------------------------------------------------|----|

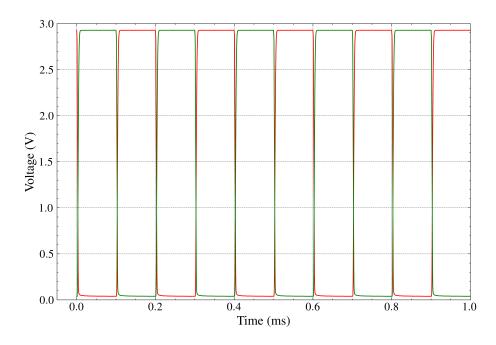

| 4.12 | Square Wave Response of the Transconductance Boosting Differential Amplifier Closed-Loop | 56 |

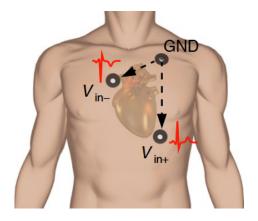

| 4 13 | Visual Representation of an ECG Signal Source                                            | 57 |

|      | Designed Test Bench for ECG Signal Simulation                                            | 57 |

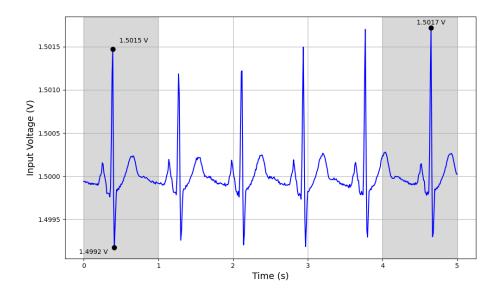

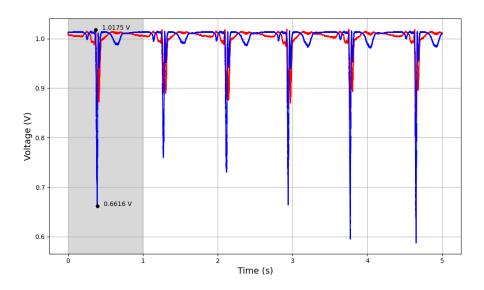

|      | Transient Representation of the ECG Signal                                               | 58 |

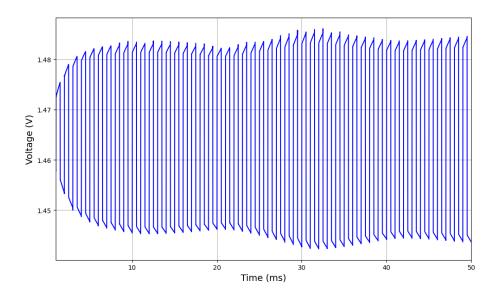

|      | Chopped Electrocardiogram                                                                | 58 |

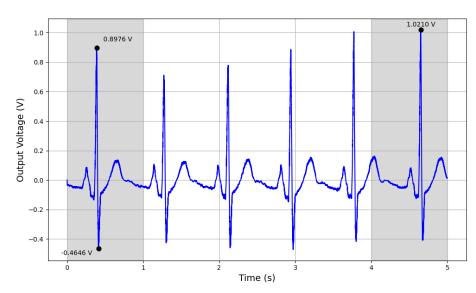

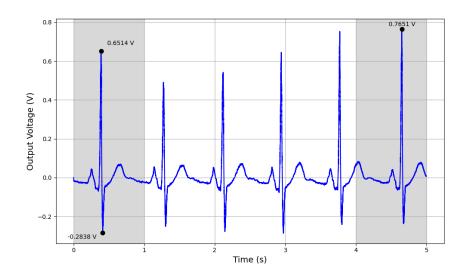

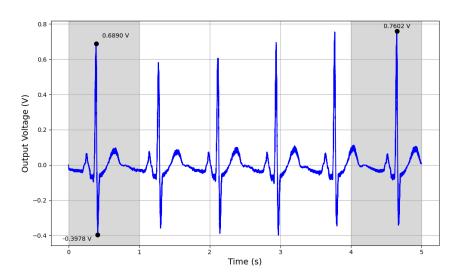

|      | Simple Differential Amplifier Output $f_{chop}$ =1 kHz                                   | 59 |

|      | Single-Ended Output Simple Differential Amplifier $f_{chop}$ =1 kHz                      | 59 |

|      | Simple Differential Amplifier Output $f=5$ kHz                                           | 60 |

|      | Single-Ended Output Simple Differential Amplifier $f_{chop}$ =5 kHz                      | 60 |

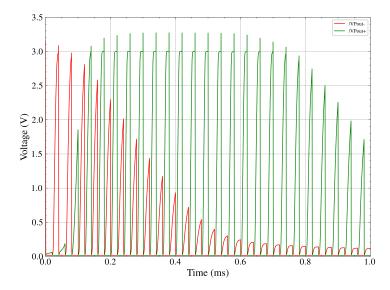

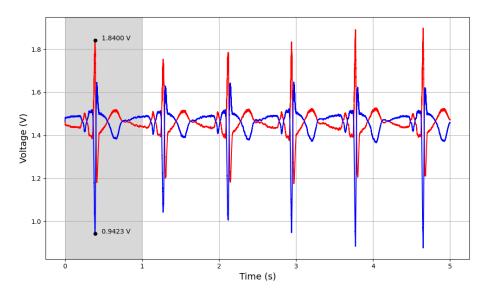

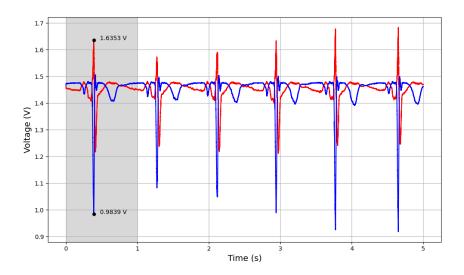

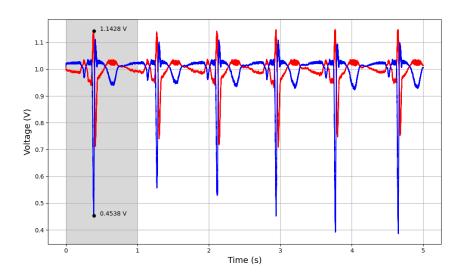

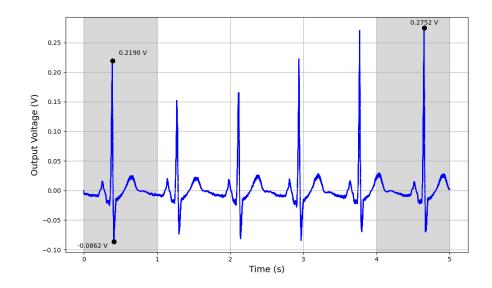

|      | Transconductance Boosting Differential Amplifier Output $f_{chop}$ =1 kHz                | 61 |

|      | Single-Ended Output Transconductance Boosting Differential Amplifier $f_{chop}$ =1 kHz   | 61 |

| 4.23 | Transconductance Boosting Differential Amplifier Output $f_{chop}$ =5 kHz                | 62 |

| 4.24 | Single-ended Output Transconductance Boosting Differential Amplifier $f_{chop}$ =5 kHz   | 62 |

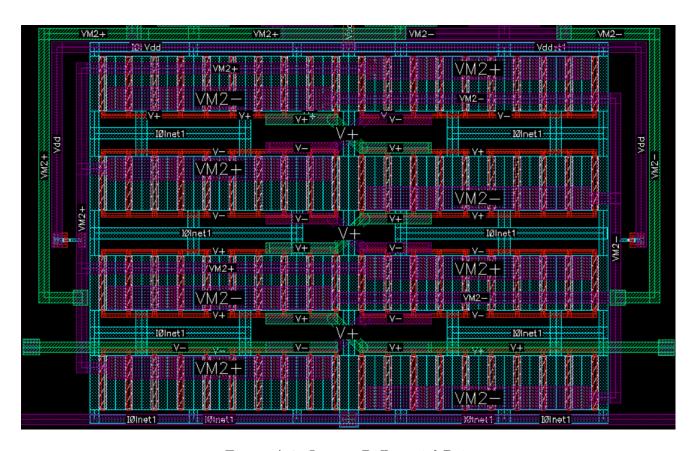

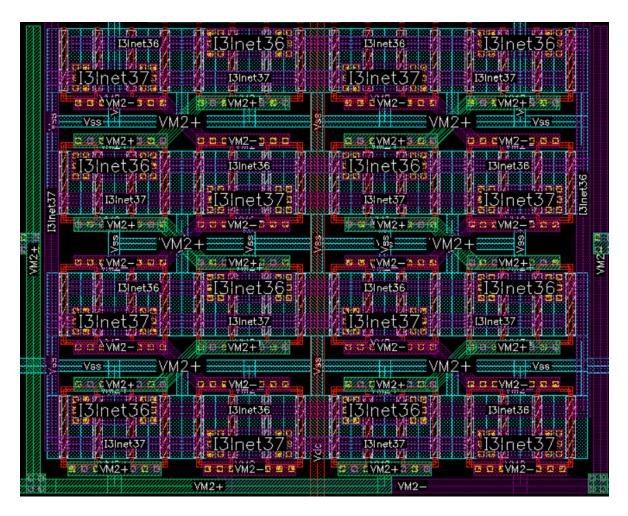

| A.1  | Layout Current Mirror                                                                    | 75 |

| A.2  | Layout Current Mirror Magnified Transistor Stack                                         | 75 |

| A.3  | Layout Differential Pair                                                                 | 76 |

| A.4  | Layout Differential Pair Magnified                                                       | 76 |

| A.5  | Layout First Amplification Stage                                                         | 77 |

| A.6  | Layout First Amplification Stage Diode-Connected Transistors                             | 77 |

| A.7  | Layout Last Amplification Stage                                                          | 78 |

| A.8  | Layout Bias Current Generation and Output Buffer                                         | 78 |

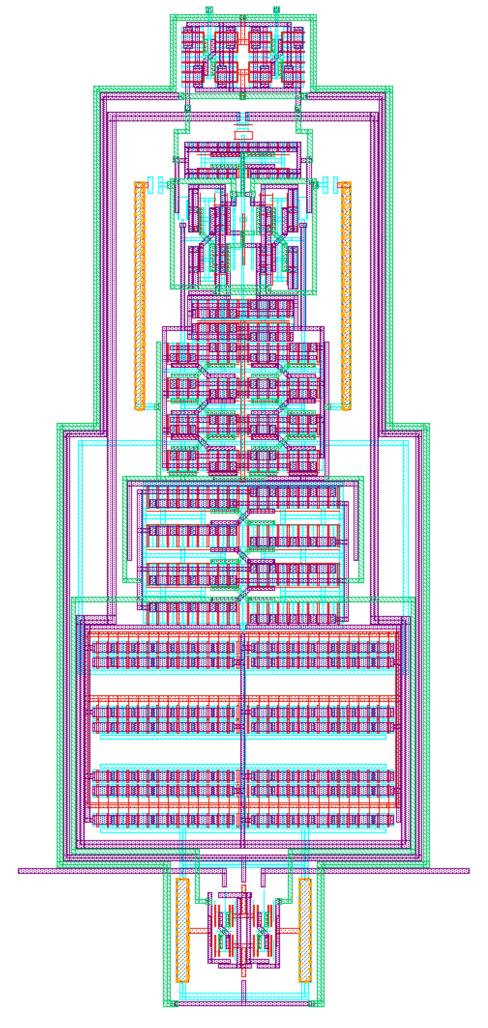

| A.9  | Chopping Amplifier Layout                                                                | 79 |

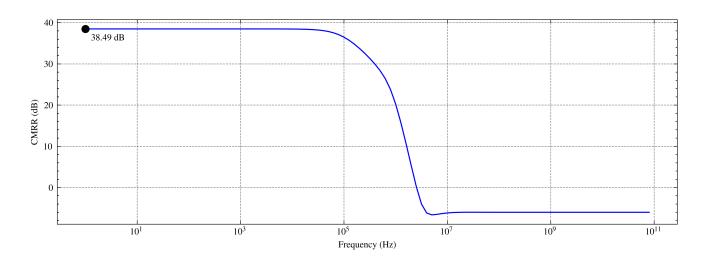

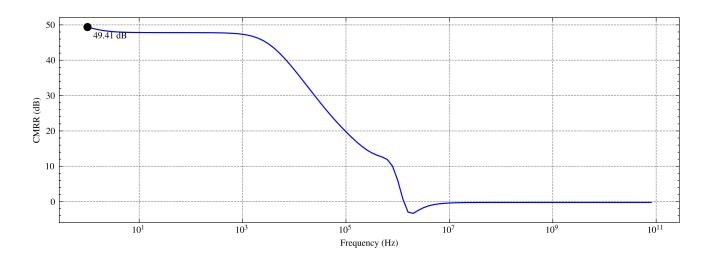

| C.1  | CMRR Simple Differential Amplifier Closed-Loop                                           | 91 |

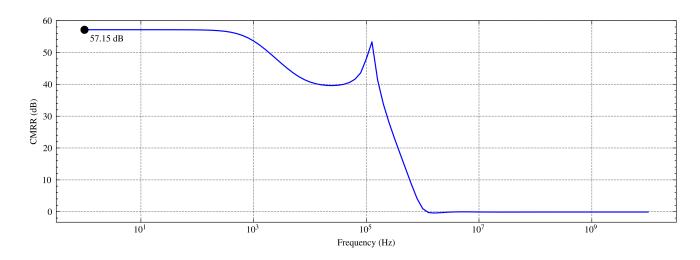

| C.2  | CMRR Diode-Load Differential Amplifier Open-Loop                                         | 91 |

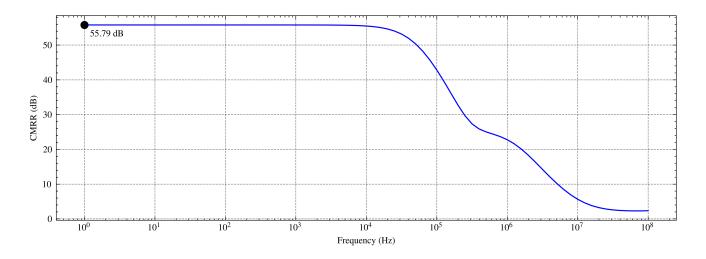

| C.3  | CMRR Bootstrapped Differential Amplifier                                                 | 92 |

| C.4  | CMRR Transconductance Boosting Differential Amplifier                                    | 92 |

| D.1  | Diode-Load Differential Amplifier Without Miller Compensation                            | 93 |

| D.2  | Bootstrapped Differential Amplifier Without Miller Compensation                          | 93 |

| D.3  | Transconductance Boosting Differential Amplifier Without Miller Compensation .           | 94 |

| E.1  | Ripple on Output Differential Amplifier                                                  | 95 |

# Acronym List

**OPAMP** Operational Amplifier

ECG Electrocardiogram

CMRR Common-Mode Rejection Ratio

PM Phase Margin

**AFE** Analogue Front-End

CMOS Complementary Metal-Oxide-Semiconductor

**TFT** Thin-Film Transistors

LTPS Low-Temperature Polycrystalline Silicon

**a-Si** Amorphous Silicone

a-IGZO Amorphous Indium-Gallium-Zinc-Oxide

**CS** Common-Source

**CG** Common-Gate

**CM** Common-Mode

UGBW Unity Gain Bandwidth

**SDA** Simple Differential Amplifier

**DCDA** Diode Connected Differential Amplifier

BDA Bootstrapped Differential Amplifier

**TBDA** Transconductance Boosting Differential Amplifier

**ADC** Analogue to Digital Converter

# Abstract

The field of flexible electronics is gaining increasing interest due to its wide applicability in society, including the recording of electrocardiograms (ECG) using a flexible patch. The amplification of the heart signal is essential to enable an accurate ECG recording. The focus of this master's thesis is on the design of an operational amplifier (OPAMP) that can be integrated on a flexible chip made from indium gallium zinc oxide (IGZO), with the aim of improving the accuracy and quality of the ECG signal processing.

The OPAMP was designed using a 600nm IGZO TFT process technology node of the PragmetIC Semiconductor foundry. The designed OPAMP utilizes chopping to suppress noise. Furthermore, an ECG signal obtained from a medical study is applied to the OPAMP, to evaluate its performance in real-time signal amplification.

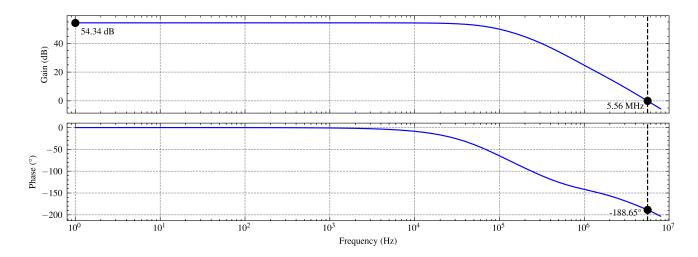

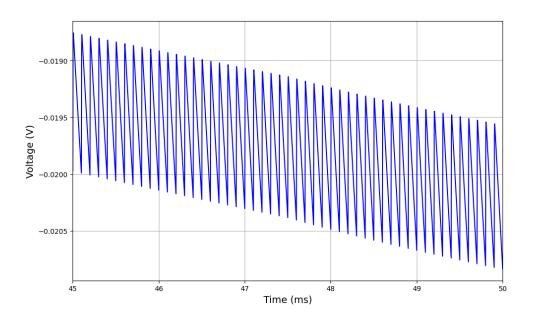

The OPAMP operates with a supply voltage of 3 V and achieves a gain of 54.34 dB. The common-mode rejection ratio (CMRR) is 57.15 dB, with a total system bandwidth of 425.25 kHz. The phase margin is measured at  $60^{\circ}$ , indicating a stable system, with a total power consumption of 106.3  $\mu$ W. The results show that the OPAMP is suitable for use in a flexible patch. Moreover, the noise-suppressing techniques enhance signal quality and accuracy with a small compromise in the gain. The obtained signal contains a small ripple, which can be addressed in future research.

# Abstract in Dutch

Flexibele elektronica kent toenemende belangstelling vanwege de brede toepasbaarheid in de samenleving, waaronder het registeren van elektrocardiogrammen (ECG) met behulp van een flexible pleister. Voor het opnemen van een ECG is het versterken van het hartsignaal essentieel. Deze masterproef richt zich op het ontwerpen van een operationele versterker (OPAMP) geïntegreerd op flexibele chip gemaakt van indium-gallium-zinkoxide (IGZO), met het doel de kwaliteit en accuraatheid van de ECG-signaalverwerking te verbeteren.

Voor het ontwerpen van de OPAMP wordt de 600nm IGZO TFT technologie van PragmatIC Semiconductors gebruikt. De ontworpen OPAMP maakt gebruik van chopping om ruis te onderdrukken. Daarnaast wordt er een ECG-signaal van een medische studie aangelegd op de OPAMP, om de prestatie ervan te evalueren op het gebied van realtime signaalversterking.

De ontworpen OPAMP functioneert bij een voedingspanning van 3 V en behaalt een versterking van 54,34 dB. De common-mode rejection ratio (CMRR) bedraagt 57,15 dB, waarbij de totale bandbreedte van het systeem 425,25 kHz bedraagt. Het systeem verbruikt 106.3 µW, met een fasemarge van 60°. De bekomen resultaten tonen aan dat de OPAMP geschikt is voor een toepassing in een flexibele pleister. Bovendien dragen de ruisonderdrukkende technieken bij aan een verbeterde signaalkwaliteit en accuraatheid, ten koste van een minimale afnamen in versterking. Het bekomen signaal bevat een kleine rimpel, waarvoor toekomstig onderzoek kan uitwijzen hoe deze het beste weggewerkt kan worden.

# Chapter 1

## Introduction

### 1.1 Motivation

Technological advancements have significantly impacted human health care [1], with the two fields becoming increasingly intertwined, as evidenced by recent developments involving artificial intelligence (AI) and wearable devices. These wearable devices can be developed with thin-film transistors (TFTs), which can conform to the shape of the patient's body. Such systems enable diagnosis from virtually anywhere [2],[3]. These rely on continuous collection of critical physiological data such as heart rate, blood pressure, body temperature, among other parameters.

Such information can be obtained by using Analogue Front-End (AFE) circuits, which convert the analogue data to digital formats that can be processed and interpreted by an AI model or medical expert. These circuits need low-noise, high-gain amplifiers to enhance the resolution and peak voltage, thereby ensuring accurate and reliable data acquisition. To achieve the low-noise aspect, an Operational Amplifier (OPAMP) is commonly used. These components are designed to amplify the difference between two input signals, which facilitates suppression of common-mode noise present on both inputs, thereby improving signal quality.

Accurate signal processing at hardware level is not only necessary for a correct diagnosis but also for enabling the early detection of various medical conditions [4],[5].

## 1.1.1 Emerging Technologies, Systems and Security

The Emerging Technologies, Systems and Security (ES&S) [6] research group at KU Leuven researches secure and efficient hardware implementations for both flexible and silicon-based electronics. One of their ongoing studies focuses on the integration of AI into flexible chips, a promising approach for applications in clinical trials, as previously discussed. In this context, there is a need to analyse an electrocardiogram (ECG), a time-dependent representation of the heart's electrical activity [7], that can be achieved through the implementation of an AFE.

The research group works with PragmatIC to create the flexible wafers in Amorphous Indium Gallium Zinc Oxide (a-IGZO) technology, as demonstrated in the GRASP project [8]. Overall, a-IGZO transistors are preferred because of their lower leakage current and lower production cost compared to other thin-film transistors [9].

### 1.2 Problem Statement

#### 1.2.1 Electrocardiogram Signals

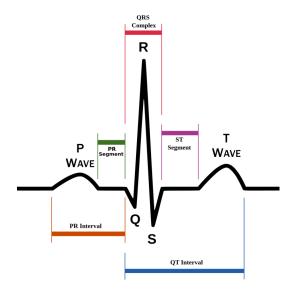

The heart contracts due to the polarization of the heart muscle fibre membranes [10], which can be detected on the skin's surface by placing 12 leads in different locations. A less accurate, yet more practical approach is the single-lead implementation, which is particularly advantageous for integration on flexible substrate. Figure 1.1 shows a visual representation of such a signal.

Figure 1.1: Visual Representation of an ECG Signal [11, p. 181]

This signal consists of multiple intervals with varying amplitudes, each corresponding to the depolarization of different parts of the heart muscle. The lowest amplitude ranges between 1.0 and 1.4 mV for healthy males and 0.7 to 1.0 mV for healthy females [12]. Additionally, these signals have a low driving capability, meaning they are unable to effectively drive circuits with a low input impedance.

#### 1.2.2 Noise Sources

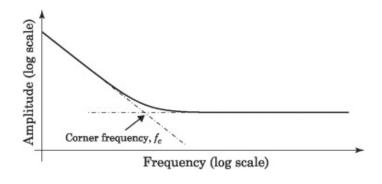

It has been established that active components and resistors are primary noise sources within an electronic system. The two predominant categories are white and 1/f noise. White noise is characterized by its presence across all frequencies, while 1/f noise is limited to a certain corner frequency. Figure 1.2 displays the 1/f and white noise elements in relation to the frequency.

Figure 1.2: White and 1/f Noise in Function of Frequency [13, p. 123]

White or thermal noise is attributed to the pseudo-random movement of free carriers within the material [14], and is solely dependent on the material's temperature. Additionally, these carriers move to eliminate the electrical fluctuation created by the black body radiation. The power created due to white noise is modelled by Equation 1.1 [15].

$$P_{noise} = 4kTB \tag{1.1}$$

Equation 1.1 shows that white noise can be calculated using the temperature of the material T, the Boltzmann constant, and the bandwidth of the system B.

The most prevalent noise at lower frequencies is the 1/f noise, which is believed to be created from trapping and releasing free carriers within the material's oxide traps [16]. These can be created by defects in the a-IGZO atomic structure, with oxygen vacancies being a known example [17]. The trapped free carriers can not participate in current transport and therefore cause noise.

The time constant, denoted by  $\tau$ , of each trap determines the duration of charge trapping  $(\tau_+)$  and releasing  $(\tau_-)$ . The magnitude of the time constants characterizes the classification of traps as either slow or fast [18]. If the period of the signal is shorter than the time required for the trap to capture a charge carrier, then the capture process will be inhibited [19]. This shows that, at higher frequencies, a reduced number of traps become available to trap charge carriers.

#### 1.2.3 Material Constraints

The ECG signal comprises a range of frequencies from 0 to 100 Hz [12], placing it within the 1/f noise spectrum of a-IGZO transistors. The noise created by a-IGZO transistors exhibits a maximum power spectral density of  $10^{-18}A^2/Hz$  [20], which is lower than other TFT technologies [21]. This indicates that the OPAMP itself will introduce noise into the amplified signal, which reduces the resolution. If not properly accounted for, noise may be misinterpreted by the AI model or medical professionals as an early indicator of a medical condition in clinical applications.

a-IGZO technology has a low hole mobility due to the intrinsic characteristics of the material [22], which prevents the practical use of PMOS transistors, and by extension, the implementation of complementary metal-oxide-semiconductor (CMOS) circuits. As a result, the OPAMP must be constructed exclusively with NMOS transistors, limiting the achievable gain.

Since the OPAMP is intended for use on a flexible patch, its power consumption must also be strictly limited. This is necessary to enable remote usage of the patch and to ensure the patients safety.

## 1.3 Objectives

The primary objective of this masters thesis is to design and implement the amplification stage of an AFE, with the goal of achieving high amplification and low noise, whilst preserving the critical information and signal structure. This goal can be divided into several sub-objectives.

The first objective involves the use of an OPAMP to improve the Common-Mode Rejection Ratio (CMRR). This is achieved by a differential pair, which needs to be carefully optimized to provide additional amplification while maximizing the CMRR. The initial amplification stage plays a

critical role in determining the overall noise performance, as it predominantly governs the extent to which noise is amplified throughout the system.

The second objective is to ensure that the output of the differential pair is amplified without compromising the stability of the system. This enables the provision of feedback to the system, while preventing oscillation from occurring.

The third objective ensures that noise created by the system itself is removed or lowered. This creates a clean output signal suitable for accurate digital conversion. Finally, a high input impedance is essential in the amplifier to prevent loading the ECG signal source. This creates an accurate voltage measurement without signal attenuation.

### 1.4 Method

#### 1.4.1 Differential Stage

The OPAMP was designed using the PragmatIC 600 nm technology for a-IGZO within the Virtuoso Cadence simulation environment. This tool facilitates both schematic circuit design and physical layout implementation. Additionally, the simulator includes a built-in local optimization feature, which enables automated adjustment of transistor sizing to meet specified target values for predetermined performance parameters. The differential stage was optimized for a high CMRR while maintaining an appropriate level of voltage amplification.

## 1.4.2 Amplification Stage

To improve the gain further, a cascaded amplifier will be added at the output. The stability of a system is characterized by the Phase Margin (PM). Which is defined as the difference between measured phase angle and 180° when the amplification is 0 dB [23]. To ensure that the system does not oscillate whilst having a usable settling time, the PM should be between 45° and 70° [24].

## 1.4.3 Chopping

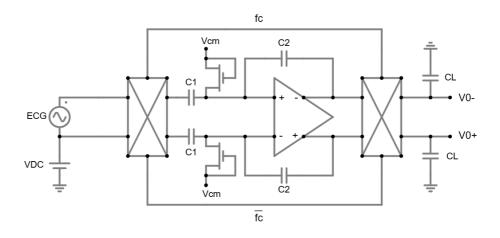

To mitigate noise introduction by the system itself, a technique known as chopping is implemented. This method involves translating the input signal to a frequency above the 1/f noise corner, thereby significantly reducing the low-frequency noise component [25]. This frequency translation is achieved through the use of mixers, which may be implemented in either active or passive configuration [26]. To lower power consumption and reduce system complexity, the passive mixer configuration is selected for this work. These mixers perform modulation of the input signal around a specified frequency, which is set to 1 or 5 kHz in the context of this master's thesis. After modulating, the signal is amplified and subsequently demodulated, with the gain preserved throughout the process.

## 1.5 Thesis Outline

This masters thesis is divided into 5 different chapters, with each addressing a specific aspect of the research:

- Second chapter: examines the advantages of a-IGZO over alternative TFT technologies. Furthermore, it investigates various OPAMP design approaches relevant to the context of IGZO-based circuits and low noise applications.

- Third chapter: discusses several amplifier architectures which are designed and explained in detail.

- Fourth chapter: discuses the different test benches used to evaluate the differential amplifiers. The results from these test benches are observed and discussed. Whereafter, the amplifiers with promising results will be tested on a chopped ECG signal.

- **Fifth chapter:** gives a short recap on what has been established and gives recommendations for future work.

# Chapter 2

# Literature Study

### 2.1 Introduction

The integration of analogue signals into digital systems is a well established concept that has been extensively studied in the literature. This is particularly true for Analogue Front-End (AFE) circuits designed for ECG signal acquisition, where implementations using materials such as a-IGZO and many others have also been explored. This chapter reviews previously implemented AFE designs and used materials to serve as a foundation for the AFE developed in this master's thesis.

## 2.2 Thin-Film Transistor Technologies

## 2.2.1 Low-Temperature Polycrystalline Silicon

Low-Temperature Polycrystalline Silicon (LTPS) is a type of polycrystalline silicone created at comparatively lower temperatures. Unlike crystalline silicon (c-Si), LTPS consists of multiple silicon grains separated by grain boundaries, which act as a potential barrier inhibits charge carrier movements and can significantly influence electrical properties [27]. Although LTPS exhibits lower conductivity compared to c-Si, it still outperforms other TFT technologies. This is reflected in an electron mobility which ranges from 50 to  $100 \frac{cm^2}{V^2s^2}$  [9]. One key advantage of LTPS is its ability to support both NMOS and PMOS transistors. However, the fabrication process of LTPS is more complex than that of a-IGZO, resulting in higher production costs [9].

## 2.2.2 Amorphous Silicone

Amorphous Silicone (a-Si) differs from its crystalline counterpart primarily in its atomic structure. Unlike crystalline silicon, which exhibits a well-ordered lattice, a-Si consists of a continuous random network. This non-crystalline configuration enables the material to maintain a solid state with mechanical stability, despite the absence of long-range atomic order [28]. However, this structural disorder significantly reduces electron mobility compared to crystalline silicon. For a-Si, typical electron mobility ranges from 0.5 to 1  $\frac{cm^2}{V^2s^2}$  [9]. Similar to a-IGZO, a drawback of this technology is the inability to effectively fabricate PMOS transistors. In comparison to a-IGZO and LTPS, a-Si has a relatively low production cost, which remains one of its primary

### 2.2.3 Amorphous Indium Gallium Zinc Oxide

a-IGZO exhibits an electron mobility in the range of 10 to 40  $\frac{cm^2}{V^2s^2}$ , and is comparatively more cost-effective to manufacture than LTPS [9]. Although its electron mobility is lower than that of LTPS, it significantly outperforms a-Si, making a-IGZO a promising material for the development of flexible integrated circuits. One notable drawback, as discussed before, is the absence of PMOS transistors.

## 2.3 Amplifiers

### 2.3.1 Single-Stage Amplifier

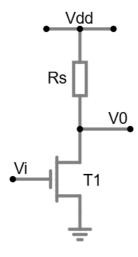

Before delving deeper in the workings of differential stages and a-IGZO-based implementations, it is essential to first understand the single-stage amplifier, as it forms the foundational building block of most amplifier architectures. Among these, the common-source (CS) amplifier is recognized as one of the three primary configurations [29]. The implementation of a CS amplifier is shown in Figure 2.1.

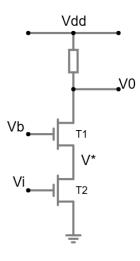

Figure 2.1: Common-Source Amplifier

To analyse the response of the output voltage  $V_0$  to variations in the input  $V_i$ , a sweep is applied at the  $V_i$  node ranging from ground to  $V_{dd}$  [30]. When  $V_i = 0$  V the transistor remains off, and  $V_0$  is pulled op to  $V_{dd}$ . As  $V_i$  approaches the threshold voltage  $V_{th}$ , transistor  $T_1$  begins conducting, leading to an increase in the drain current  $I_d$ . This rise in current results in a voltage drop across the resistor  $R_s$ , thereby reducing  $V_0$ . The current induced by changing the gate voltage  $V_g$  of a transistor operating in the saturation region is described by Equation 2.1 (if channel-length modulation is neglected), and the transconductance of the MOSFET by Equation 2.2

$$I_D = \frac{1}{2} C_{ox} \mu_n \frac{W}{L} (V_{GS} - V_{th})^2$$

(2.1)

$$g_m = C_{ox}\mu_n \frac{W}{L}(V_{GS} - V_{th}) \tag{2.2}$$

The gain of a CS amplifier is given in Equation 2.3, and is derived from [30].

$$A_v = -g_m R_s \tag{2.3}$$

Equation 2.3 indicates that the voltage gain of a CS amplifier is dependent on the transconductance of the used MOSFET and the output resistance. The negative sign in the gain expression signifies a 180° phase shift between the input and output. Furthermore, considering Equation 2.2, it becomes evident that the gain is also a function of the gate-to-source voltage  $V_{GS}$ , thereby introducing a degree of nonlinearity into the amplification behaviour.

The design of a CS amplifier involves a series of trade-offs, as each design choice affects the overall performance. Based on Equations 2.3 and 2.2 a reduction in channel length and an increase in the width of a transistor would be preferred. However, enlarging the transistor dimensions, particularly the width, would increase the input capacitance and thus introduce a greater parasitic load [30]. This added capacitance can significantly degrade the frequency response by lowering the bandwidth and limiting overall gain, particularly at high frequencies. Increasing the resistance value of  $R_s$  effects the voltage gain  $A_v$ . However, if the voltage drop across  $R_s$  approaches  $V_i - V_{th}$ , transistor  $T_1$  may be driven out of the saturation region, which limits the output swing.

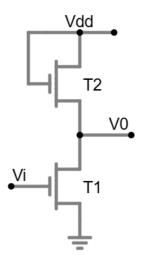

Due to limited area and achievable transistor parameters on silicon or a-IGZO substrates, the use of a diode-connected load may present a viable alternative for certain circuit configurations. Figure 2.2 depicts the implementation of a diode-connected circuit, which is characterized by the use of a diode-connected transistor instead of a resistive load.

Figure 2.2: Diode-Connected Load

Transistor  $T_2$  in Figure 2.2 will always operate in the saturation region be cause  $V_{DS} = V_{GS}$ . The gain of this circuit is obtained in [30, P. 54] and shown in Equation 2.4.

$$A_v = -g_{m1} \frac{1}{g_{m2} + g_{mb2}} (2.4)$$

In this equation,  $g_{mb2}$  accounts for the body effect of transistor  $T_2$ , which is not present in a-IGZO. Furthermore, the term  $g_{m2}$  introduces non-linearity due to the variations in  $V_{GS}$ , as the source node is connected to  $V_0$ , which itself varies with the input signal. It is important to note that the diode connected transistor could, in principle, be implemented using a PMOS device. However as stated before a-IGZO limits the use of PMOS transistors.

#### 2.3.2 Differential Amplifier

Simple single-ended amplifiers increases a signals voltage with respect to a fixed reference, whilst a differential signal is determined by the voltage between two nodes, neither of which is directly tied to ground or  $V_{dd}$  [30]. Such signals oscillate around a DC offset which is known as the common-mode voltage (CM). Signal integrity can be compromised by surrounding electromagnetic interference resulting from capacitive or inductive coupling. This issue is particularly pronounced in single-ended signals, where such interference is more challenging to mitigate. In differential signals, however, interference affects both lines similarly, thus preserving the voltage difference between them and enhancing robustness against noise [30]. Such implementations have a high common-mode rejection.

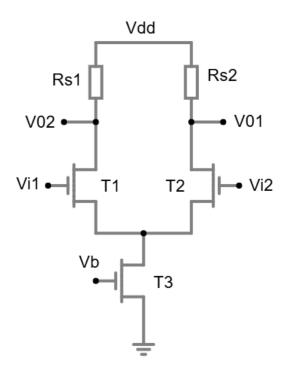

Differential amplifiers are constructed using two single-ended amplifiers and are designed to amplify the voltage difference between two signals. Figure 2.3 presents a transistor-level schematic of a differential amplifier.

Figure 2.3: Differential Amplifier Circuit

Transistor  $T_3$  in Figure 2.3, maintains a constant tail current flow, which ensures that the output CM level remains independent of the input CM voltage. A stable tail current is necessary to enhances the Common-Mode Rejection Ratio (CMRR), as it enforces Equation 2.5.

$$I_{D3} = I_{D2} + I_{D1} (2.5)$$

This equation shows that  $I_{D3}/2$  flows through  $T_1$  and  $T_2$  if both signal have the same input voltage. Consequential, a voltage value of  $V_{dd} - R_D I_{D3}/2$  will be present at both output terminals, which is equal to the output CM value. Assume that the gate voltage of transistor  $T_2$  is higher than that of transistor  $T_1$ , which causes  $T_2$  to conduct current whilst  $T_1$  remains turned off. Consequential, a current equal to  $I_{D3}$  flows through transistor  $T_2$ , producing a voltage at node  $V_{01}$  equal to  $V_{dd} - R_{s2}I_{D3}$ . As the input voltage  $V_{i1}$  increases beyond the threshold voltage  $V_{th1}$ , transistor  $M_1$  begins conducting. Due to the current coupling through  $I_{D3}$ , the current  $I_{D2}$  must decrease in order to ensure that the value of  $I_{D3}$  remains constant. This reduction in the current  $I_{D2}$  decreases the voltage drop over  $R_{s2}$ , thereby increasing the voltage at node  $V_{02}$ . As  $I_{D1}$  increases to a value equal to  $I_{D3}$ , causing  $I_{D2}$  to become sufficiently low causing transistor  $T_2$  to be turned of [30].

The maximum output voltage swing of a differential amplifier starts from  $V_{dd}$  to  $V_{in,CM} - V_{th}$  as described in [30, p. 106]. This implies that  $V_{in,CM}$  needs to assume the lowest possible value. To ensure that  $I_{D1}$  and  $I_{D2}$  won't influence the  $I_{D3}$  current, transistor  $T_3$  needs to operate in the saturation region and Equation 2.6 needs to be met. The lowest possible value of  $V_{in,CM}$  can be derived from the following equations.

$$V_{DS3} \ge V_{GS3} - V_{th3}$$

(2.6)

$$V_{DS3} = V_{D3} - 0V = V_{S1} - 0V (2.7)$$

$$V_{GS1} = V_{G1} - V_{S1} <=> V_{S1} = V_{G1} - V_{GS1}$$

(2.8)

If the gate voltage of transistor  $T_1$  is equal to  $V_{in,CM}$  then:

$$V_{S1} = V_{in,CM} - V_{GS1} (2.9)$$

Substituting Equation 2.9 into 2.6, Equation 2.10 can be obtained [30].

$$V_{in,CM} \ge V_{GS1} + (V_{GS3} - V_{th3}) \tag{2.10}$$

Where equation 2.10 shows the minimum common-mode input voltage that can be used for a given differential amplifier. The amplification that can be achieved is determined by the small signal analyses in [30] and can be found in Equation 2.11.

$$\frac{(V_x - V_y)}{(V_{i1} - V_{i2})} = -g_m R_s \tag{2.11}$$

#### 2.3.3 Current Mirror

Equation 2.1 holds under the condition that  $V_{DS} \geq V_{GS} - V_{th}$ , indicating that NMOS transistors are well-suited for use as a current source. In the saturation region, the drain current remains effectively constant with respect to variations in the drain-source voltage, provided that channel-length modulation if neglected. Under these assumptions, the current is primarily governed by the gate-source voltage. Since the current through transistor  $T_1$  remains constant despite variations in the voltage across it, the transistor can be modeled as a high output impedance. A transistor level representation of a current mirror is depicted in Figure 2.4.

Figure 2.4: Current Mirror Circuit

In the configuration shown in Figure 2.4, the current present at  $I_2$  is copied to transistor  $T_1$ . which can be calculated with Equation 2.12 [30].

$$I_1 = \frac{(W/L)_1}{(W/L)_2} I_2 \tag{2.12}$$

This demonstrates that the copied current is determined solely by the reference current and relative sizing of the transistors. To reduce overall current consumption, the transistors can be proportionally scaled such that the reference current,  $I_2$ , is a factor  $\frac{(W/L)_2}{(W/L)_1}$  smaller than the desired output current. To ensure that even with system variation the ratio between the two transistors remains the same, it is common practice to use a unit transistor with fixed width and length. To achieve the desired scaling, these unity transistors can be placed in parallel or series, thereby effectively increasing the width or length of the overall device while preserving matching characteristics. If the channel-length modulation is taken into account then Equation 2.12 is changed to Equation 2.13.

$$I_1 = \frac{(W/L)_2}{(W/L)_1} \frac{1 + \lambda V_{DS2}}{1 + \lambda V_{DS1}} I_2$$

(2.13)

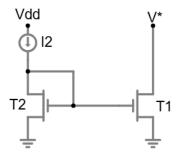

Due to the channel-length modulation the current trough transistor  $T_1$  wont be equal to the reference, unless  $V_{DS1} = V_{DS2}$ . Due to fluctuations in  $V^*$  this condition cannot always be met. Therefore, some techniques have been created to mitigate this effect [30, pp. 140-145]. As described earlier both drain-source voltages need to be equal to each other, which can be forced by the usage of cascoding transistors. Figure 2.5 illustrates both solutions.

Figure 2.5: Cascoding Current Mirror [30, p. 145]

To ensure that both drain-source voltages of transistor  $T_1$  and  $T_2$  are equal,  $V_{DS1}$  can be forced to be equal to  $V_{DS2}$ , or vice versa. A circuit which forces  $V_{DS2}$  to be equal  $V_{DS1}$  is shown in Figure 2.5 (a) and is know for having headroom problems, if  $V^*$  is lower than a given value. The lowest value that  $V^*$  can obtain is calculated starting from Equation 2.14.

$$V_{DS0} \ge V_{GS0} - V_{th} \tag{2.14}$$

Because both source voltages are equal, Equation 2.14 and be written as:

$$V_{D0} \ge V_{G0} - V_{th} \tag{2.15}$$

$$V_{G0} = V_{D0} = V_{DS0} + V_{DS2} = V_{GS0} + V_{GS2}$$

(2.16)

When Equation 2.16 is substituted into Equation 2.15 then:

$$V^* = V_{G0} - V_{th} = V_{GS0} + V_{GS2} - V_{th} (2.17)$$

Which is the lowest value  $V^*$  can obtain to ensure that transistor  $T_3$  and  $T_4$  are not driven out of saturation. To avoid a part of this headroom issue the circuit in Figure 2.5 (b) is proposed, where  $V_{DS1}$  is forced to be equal to  $V_{DS2}$ . If assumed that  $V_{GS0} = V_{GS3}$  then the following equations proves that  $V_{DS1} = V_{DS2}$ .

$$V_{S0} = V_b - V_{GS0} (2.18)$$

$$V_{DS2} = V_{D2} - V_{S2} = V_{S0} - 0V = V_b - V_{GS0} = V_{DS1}$$

(2.19)

Now  $V_b$  needs to be chosen to ensure that transistor  $T_0$  and  $T_2$  are in saturation and can be calculated by Equation 2.20 [30, P. 144].

$$V_{GS0} + (V_{GS1} - V_{th}) \le V_b \le V_{GS1} - V_{th0} \tag{2.20}$$

The bias voltage  $V_b$  can be generated using transistors  $T_4$  and  $T_5$ , where  $T_5$  establishes the required overdrive voltage and  $T_4$  sets the corresponding gate-source voltage  $V_{GS}$ . This ensures that  $V_b$  is equal to  $V_{GS1} - V_{th}$ .

## 2.4 Improving Gain

The gain of an OPAMP is influenced by several factors, including the supply voltage, bias current, output impedance, input impedance, and other circuit-level parameters. Therefore, numerous design techniques have been proposed to ensure stable gain performance over a broader frequency spectrum.

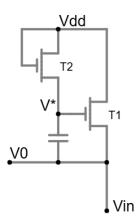

### 2.4.1 Bootstrapping

As mentioned before, the output impedance plays a crucial role in the gain of an OPAMP. One technique used to improve the output impedance is the bootstrapping circuit. It operates by maintaining a constant voltage across specific circuit elements, thereby ensuring a steady current through those elements even as the overall node voltage fluctuates. As a result, the circuit appears to exhibit a higher output impedance. A bootstrapping circuit to achieve this is shown in Figure 2.6.

Figure 2.6: Bootstrapping Circuit

The bootstrapping circuit boosts the voltage at a given node to a value which exceeds the power supply voltage [30], utilizing positive feedback through a capacitor. It establishes a constant current by dynamical raising  $V^*$ . When the circuit shown in figure 2.6 starts up, the output voltage  $V_0$  is initially zero, causing the capacitor to charge to  $V_{dd} - V_{th}$ . As  $V_0$  increases to  $V_{dd}$ , the voltage at node  $V^*$  correspondingly rises to  $V_{dd} + V_c$ , where  $V_c$  represents the voltage contributed by the stored charge on the capacitor, which in this explanation is  $V_{dd} - V_{th}$ . As discussed before, Equation 2.1 describes the current through the drain of a transistor due to a voltage difference between the gate and source, where  $V_{GS}$  can be expressed as  $V_G - V_S = V^* - V_0$ , and since  $V^* = V_0 + V_c$ , substitution into the drain current equation yields the following expression:

$$I_D = \frac{g_m}{2} * V_C \tag{2.21}$$

This demonstrates that the current dependents solely on the voltage storred on the capacitor. If this voltage remains constant, then the current flowing through the transistor will also be constant.

## 2.4.2 Cascoding

The implementation of a cascoding stage will lower the effect of the Miller capacitor, which will be discussed later, and adds an extra output resistance, thereby increasing the gain and bandwidth. Such a stage can be realized by cascading a common-source (CS) with a common-gate (CG) transistor, where the CS transistor will convert a voltage into a current whilst the CG simply routes the signal through the system. The cascoding stage offers several advantages. However, it also presents certain drawbacks. Such an amplifier is presented in Figure 2.7.

Figure 2.7: Cascoding Amplifier

One of the key advantages of the cascode amplifier is an increase in the output resistance, which results from the additional resistance and transconductance introduced by the added transistors [30]. he output resistance of the amplifier shown in Figure 2.7 can now be written as:

$$R_{out} = [1 + (g_{m1} + g_{mb1}) * R_{01}] * R_{02} + R_{01}$$

(2.22)

If  $g_m * R_0 >> 1$ , the output resistance  $R_{out}$  can be approximated as  $(g_{m1} + g_{mb1})R_{01}R_{02}$ , which indicates that the output impedance of transistor  $T_2$  is effectively amplified by a factor of  $(g_{m1} + g_{mb1})R_{01}$ . To ensure complete signal transfer and proper operation of the circuit, it is essential that both transistors remain in the saturation region. Consequently, a cascode amplifier exhibits a minimum output voltage determined by the sum of the saturation voltages of the two transistors, which is approximately equal to twice the overdrive voltage. It is important to note that the body effect in a-IGZO can be ignored.

Before analysing how a cascode amplifier mitigates the Miller effect, it is essential to first develop a clear understanding of the effect itself. The Miller effect explains how the input capacitance can be increased due to the achieved amplification. Where the input impedance can be calculated by equation 2.23 [31, p. 725].

$$C_{in} = C_{GS} + C_{GD}(1+A) (2.23)$$

The voltage gain associated with transistor  $T_2$  can be presented as  $\Delta V^*/\Delta V_i$ . The variation in current through a transistor is determined by Equation 2.24. Given that transistor  $T_1$  and  $T_2$  are connected in series, they share the same current flow. This relationship leads to the formation of Equation 2.25.

$$\Delta I = \frac{g_m}{2} (\Delta V_G - \Delta V_S) \tag{2.24}$$

$$g_{m1}(\Delta V_B - \Delta V^*) = g_{m2}(\Delta V_i - 0V)$$

(2.25)

Since  $V_b$  is a DC voltage, its small-signal variation  $\Delta V_b$  is zero. When both sides of equation 2.25 is divided by  $\Delta V_i$ , then the gain associated with transistor  $T_2$  can be expressed as:

$$\frac{\Delta V^*}{\Delta V_i} = -\frac{g_{m2}}{g_{m1}} = A \tag{2.26}$$

This demonstrates that the voltage swing of node  $V^*$  is reduced relatively to  $V_0$ , leading to a corresponding reduction in the Miller effect.

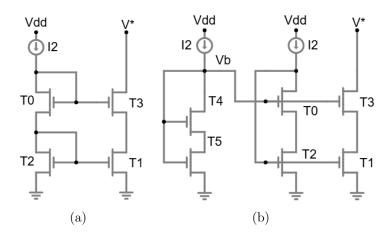

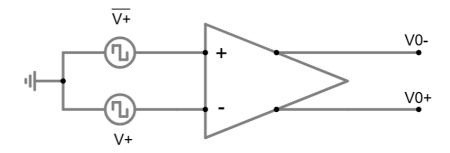

## 2.5 Chopping

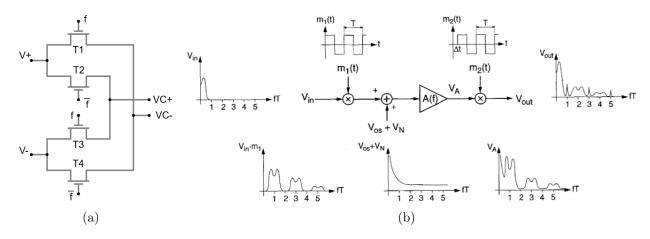

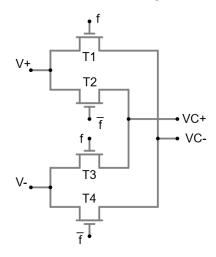

As discussed in Chapter 1, chopping is a signal modulation technique employed to shift the signal spectrum above the 1/f corner frequency, thereby mitigating the impact of low-frequency noise [32]. Figure 2.8 (a) shows a modulation circuit, called a chopper and 2.8 (b) shows the theoretical implementation.

Figure 2.8: (a) Chopping Modulation Circuit (b) Theoretical Implementation [33, p. 1590]

In Figure 2.8 (a), the symbols f and  $\bar{f}$  represent square waves with a frequency selected to exceed to 1/f noise corner and to prevent aliasing, where  $\bar{f}$  is the digital complement inverse of f. This configuration enables the combination of transistor  $T_1$  and  $T_3$  as well as  $T_2$  and  $T_4$  to be active separately. This results in the periodic presence of  $V_+$  and  $V_-$  at the outputs  $V_{C+}$  and  $V_{C-}$  [34], where the output signals can be mathematically write as:

$$V_{c-}(t) = (V_{+}(t) - V_{-}(t)) \frac{4}{\pi} \left[ \cos(\omega_{CHOP}t) - \frac{1}{3}\cos(3\omega_{CHOP}t) + \frac{1}{5}\cos(5\omega_{CHOP}t) - \cdots \right]$$

(2.27)

$$V_{c+}(t) = (V_{-}(t) - V_{+}(t)) \frac{4}{\pi} \left[ \cos(\omega_{CHOP}t) - \frac{1}{3}\cos(3\omega_{CHOP}t) + \frac{1}{5}\cos(5\omega_{CHOP}t) - \cdots \right]$$

(2.28)

Equation 2.27 demonstrates that chopping introduces harmonic frequency components, which can degrade the signal integrity. After demodulation, as illustrated if Figure 2.8 (b), the 1/f noise is translated to a frequency beyond the bandwidth of the input signal. These high-frequency components, including the shifted 1/f noise and harmonic frequencies, can subsequently be attenuated through the implementation of a low-pass filter.

It has to be noted that the implementation of chopping can itself introduce additional noise and variability into the system. This is primarily due to the capacitive coupling that exists between the various terminals in a transistors [33]. As the transistors switch at the chopping frequency f, the associated parasitic capacitances are periodically charged and discharged, leading to phenomena such as clock feedthrough. This effect can appear as an unwanted signal components at the output.

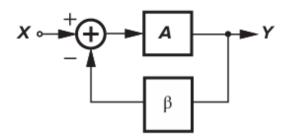

### 2.6 Feedback

Like many other electronic system differential amplifiers are subjected to system variability, which can arise due to manufacturing inaccuracies, temperature fluctuation, power supply variation and other environmental or process-related influences [30]. Therefore, feedback can be added to ensure an amplification which is not dependent on the transconductance of the system, but rather by a more stable component. There are two main feedback types, positive and negative feedback. With positive feedback the output signal is added in phase with the input signal, which can increase the gain, but pushes the system further to instability. With negative feedback, the output signal is added to the input signal with a 180° degree phase shift, effectively subtracting the output signal from the input. Such a negative feedback system is shown in Figure 2.9. The phase margin of a feedback system is defined as the difference between the phase shift introduced by the system and 180°, measured at the frequency where the loop gain magnitude equals unity. If the phase shift reaches 180°, negative feedback becomes positive feedback, potentially leading to instability.

Figure 2.9: Negative Feedback System [30, p. 276]

In Figure 2.9, the symbol A represents the open-loop gain of the system and  $\beta$  the feedback factor. The systems amplification can be obtained with Equation 2.29 [30] and is called the closed loop-gain.

$$\frac{Y}{X} = \frac{A}{1 + \beta A} \tag{2.29}$$

It can be observed that increasing  $\beta A$  reduces the systems overall dependence on the open-loop gain. To further understand this topic, a system without feedback is considered, effectively changing the transfer function to  $Y = A \cdot X$ . In this open-loop amplification, any variation in A will effected the output by the same factor. However, when negative feedback is applied, this variation also appears in the denominator of the closed loop transfer function, effectively lowering its effect on the output.

# 2.7 Bio-Potential Amplifiers

#### 2.7.1 CMOS

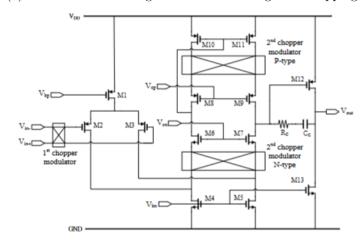

Most OPAMPs fabricated in c-Si are single-ended outputs, meaning that the signal is amplified with respect to ground. [35] proposes the system presented in Figure 2.10 and shows that the AFE amplifier uses three OPAMPs, chopping, and auto-zeroing. Where auto-zeroing is used to mitigate the effect of white noise on the system [36].

(a) Three-OPAMP Design with Auto Zeroing and Chopping

(b) Chopping OPAMP Transistor Level

Figure 2.10: CMOS ECG Amplifier [35, p. 328]

The presented amplifier can be divided into two subsections, with each a specific purpose:

- **First stage:** which is represented by two OPAMPs with their feedback interconnected forming a fully differential amplifier. In this arrangement, each amplifier amplifies its input signal relative to the output of the other, effectively amplifying the voltage difference between the two inputs.

- Second stage: this stage amplifies the difference of both signal, thereby enhancing the CMRR while providing additional gain. The resistance  $R_6$  can be used to normalize the output, ensuring that it remains within a specified voltage range.

This circuit operates with a 1.2 V power supply and consumes 1.32 mW of power. It achieves a voltage gain of 40.09 dB with a bandwidth of 69 kHZ, whilst having CMRR exceeding 60 dB. The chopping and auto-zeroing mechanisms require a external clock signal, operating at frequencies of 10 and 20 kHZ, respectively.

Certain circuit configurations have been engineered wherein a network of NMOS transistors are employed to emulate the operational characteristics of a PMOS transistor. [37] presents an OPAMP which employes pseudo-CMOS elements to implement feedback. The proposed OPAMP operates at a supply voltage of 5 V, achieving a voltage gain of 22.5 dB and consuming 160  $\mu$ W of power.

## 2.7.2 Unipolar MOS

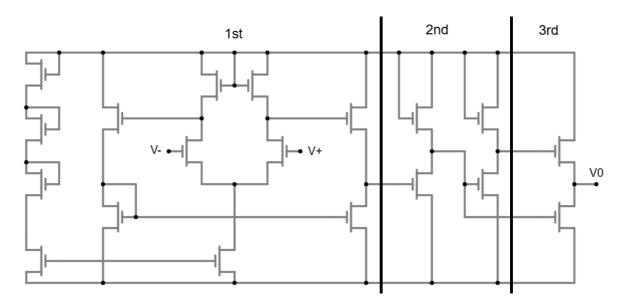

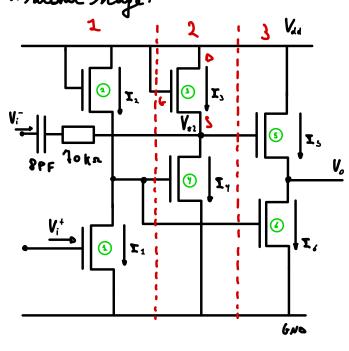

Due to the unavailability of PMOS transistors during the early development of OPAMPs, extensive research was conducted on circuits utilizing only NMOS transistors. Early studies report that a voltage gain of up to 50 dB can be achieved with a 30 V supply voltage [38]. For implementation in a-IGZO, a three stage amplifier architecture is proposed in [39], as illustrated in Figure 2.11.

Figure 2.11: NMOS Only OPAMP Design [39, p. 657]

Figure 2.11 visually separates the three stages using bold black lines. The function of each stages is described as follows:

- First stage: uses a differential pair with a constant current source, to improve the CMRR of the OPAMP. The constant current source is configured as a current mirror, ensuring stable current flow that remains unaffected by variations in the system's load [40]. The output of the differential pair is connected to a differential-to-single-ended converter, where the current delivered to the second stage is determined by the output of the differential pair. It has to be mentioned that due to the use of NMOS transistors, the maximum output voltage swing is limited to  $V_{dd} V_{th}$  [30, P. 55].

- **Second stage:** is formed from a basic cascaded amplifier, ensuring the necessary amplification.

• Third stage: is used as a buffer, ensuring effective signal transfer by mitigating the effects of the output impedance [39], [41]. It is characterized by a high input and a low output impedance, which facilitates impedance matching and prevents signal degradation [42],[43].

The paper reports a voltage gain of 23.52 dB, achieved with a supply voltage of 20 V and a power consumption of 51 mW. The amplifier demonstrates that the unity-gain bandwidth is achieved at 2.37 MHz, with a phase margin of 102°.

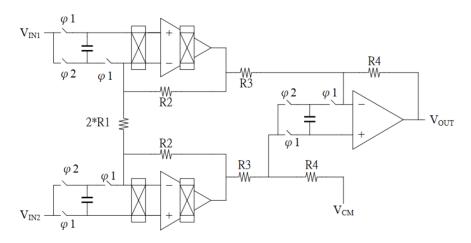

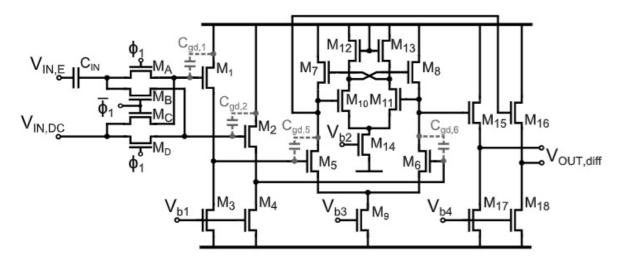

[44] proposes a fully differential amplifier, characterized by the presence of two complementary output signals. Although the differential amplifier is intended to be used for EMG signals, its architecture may serve as a valuable reference for the amplification of ECG signals as well. One notable feature of the proposed differential amplifier is the implementation of chopping at multiple frequencies, which enables the usage of a single output lead to serve an array of amplifiers. Figure 2.12 shows the proposed differential amplifier at transistor level.

Figure 2.12: Fully Differential OPAMP with Input Chopping [44, p. 144]

Figure 2.12 shows a differential amplifier with multiple embedded stage:

- $M_A M_D$ : are used to modulate the signal to a designated chopping frequency, effectively shifting it above the 1/f noise region to enhance signal integrity. In this implementation, chopping is also used to modulate individual EMG signals to distinct frequencies, allowing multiple signals to be transmitted over a single lead.

- $M_1 M_4$  and  $M_{15} M_{18}$ : are used as a buffer to ensure accurate signal transfer and to shift the signal to a preferred DC operating level.

- $M_5 M_{14}$ : uses 2 separate differential pairs, with internal feedback. Transistors  $M_{10}$  to  $M_{14}$  are used as a auxiliary amplifier, which improves the output resistance of  $M_7$  and  $M_8$  by reducing the small-signal swing.

The differential amplifier operates with a 26 V power supply and achieves a maximum voltage gain of 24.9 dB. It provides a bandwidth of 5.4 kHZ whilst maintaining a power consumption of 1.3 mW.

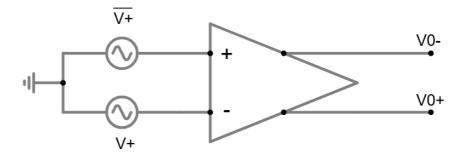

# 2.8 Analogue Front-End

An AFE is used to increase the amplitude and current of an analogue signal to a value which can be transferred into a digital signal by the use of an analogue-to-digital converter (ADC). A visual representation is provided in Figure 2.13.

Figure 2.13: Visual Representation of a Analogue Front-end [45, p. 746]

The input resolution determines the gain required from the AFE to ensure accurate analogue-to-digital conversion without signal information loss. The equation to define the minimum input voltage to achieve a bit change is defined in [46], and is shown in Equation 2.30.

$$V_{lsb} = \frac{V_{fullscale}}{2^N} \tag{2.30}$$

In this context,  $V_{LSB}$  represents the lowest input value,  $V_{fullscale}$  denotes the maximum analogue voltage value and N the resolution in bits at the output. When  $V_{fullscale}$  is equal to the supply voltage, values of  $V_{LSB}$  reported in the literature vary: [47] and [48], which use a 10 V power supply, report values of 4 mV and 19 mV, respectively. To use the full output, the ECG signal, which has an output swing between 1.0 and 1.4 mV, needs to be amplified to a maximum value of 10 V. For these ADCs a gain of 77 dB has to be realised by the AFE.

A more recent study reports the design of an ADC operating with a 4 V power supply. Allowing the AFE to have a lower gain of approximately 66 dB [49].

In addition to providing amplification, the AFE must exhibit a sufficiently high input impedance to ensure proper low-current signal transfer. [50] specifically addresses this requirement and suggest a minimum input impedance of 1.9  $G\Omega$ .

# 2.9 Conclusion

Some implementations have been discussed to increase the gain of the amplifier. However, these approaches often introduce added side effects. The state-of-the-art indicates that a-IGZO amplifiers exhibit relatively low amplification compared to Si counterparts, despite the operation at comparatively high supply voltages. These elevated supply voltages contribute to the increase in power consumption, which is undesirable for application in flexible patches, where low power operation is essential.

# Chapter 3

# **Designed Circuits**

### 3.1 Introduction

In this section of the master's thesis, various differential amplifier designs are developed and explained. Each differential amplifier discussed in this chapter shares a common current referencing circuit, which is depicted in Chapter 2, Figure 2.4. While the reference circuit remains consistent, the biasing current and size of the transistors are adjusted for each individual amplifier configuration. After covering differential amplifiers, the chopper design will be discussed.

The different transistor sizes can be obtained in one of two ways, the square-law or the  $g_m/I_d$  model. In the square-law approach, Equation 2.1 is used to calculate the current through each transistor in the system. These currents can be combined to achieve the amplification equation which is equal to  $V_{out}/V_{in}$ . With the  $g_m/I_d$  method a transistors transconductance is directly coupled to its drain current, which places a transistor in one of its three distinct regions [51]. Each region has its design trade-offs, which are shown in Table 3.1. It has to be noted that the  $g_m/I_d$  values are obtained from [52], which are measured for silicone based transistors.

Table 3.1:  $g_m/I_d$  Design Trade-offs

| regions            | Trade-off                                     | $g_m/I_d (V^{-1})$ |

|--------------------|-----------------------------------------------|--------------------|

| Weak Inversion     | Low Power, High Gain                          | 20 to 40           |

| Moderate Inversion | Moderate Gain, Moderate Speed, Moderate Power | 7 to 20            |

| Strong Inversion   | High Power, High Speed                        | 3 to 7             |

Table 3.1 outlines the appropriate operating region for a transistor based on desired design tradeoffs. In this master's thesis, the differential pairs are used in the moderate inversion region to balance the efficiency and speed, while the output stages are used in the strong inversion region to ensure high drive capability and improve linearity.

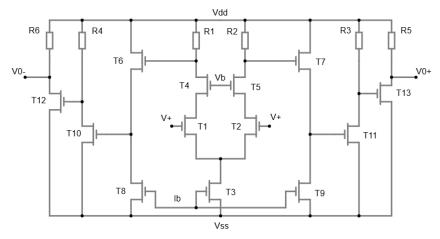

# 3.2 Simple Differential Amplifier

Due to the unipolar nature of the a-IGZO technology, which only supports NMOS transistors, the first amplifier design is relatively basic. The fundamental building blocks utilized in the circuit, shown in Figure 3.1, are based on the methodologies proposed in [30].

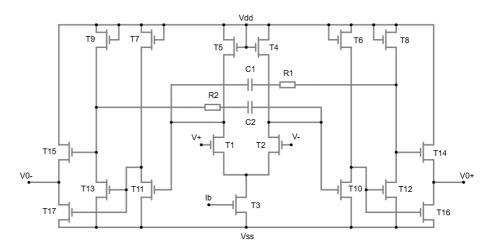

Figure 3.1: Three Stage Simple Differential Amplifier

Figure 3.1 shows a three stage differential amplifier with resistive loads, where each stage has its own purpose:

- T1-T5: ensure the common-mode functionality through the use of a shared and constant current source. Transistors T4 and T5 are configured in a cascode arrangement, as described in Chapter 2. This configuration mitigates the Miller effect, but increases the output common-mode voltage, which in turn reduces the available output swing. However, this also increases the output resistance, thereby enhancing the gain of the amplifier.

- T6-T9: lower the input voltage by  $V_{th}$ , thereby enabling a greater output voltage swing in the subsequent stages.

- T10-T13: create additional amplification. Resistors R4 and R3 are chosen to ensure that transistors T12 and T11 remain in the saturation region. Furthermore, resistor R6 and R5 are selected so that the input and output common-mode voltages are matched.

The proposed differential amplifier is designed to operate with a supply voltage of 3 V and utilizes a reference current of 3.1 µA. The bias voltage applied at the gates of transistors T4 and T5 is maintained at 2 V to ensure proper transistor operation. The different transistor sizes are shown in Table 3.2.

Table 3.2: Simple Differential Amplifier Sizes and Values

| Transistor  | $W/L (\mu m/\mu m)$ | multiplier | Resistor | $R(k\Omega)$ |

|-------------|---------------------|------------|----------|--------------|

| T1,T2,T4,T5 | 10/1.2              | 4          | R1,R2    | 1000         |

| T3,Tbias    | 5/1.2               | 7          | R3,R4    | 330          |

| T6,T7       | 1/0.6               | 1          | R5,R6    | 150          |

| T8,T9       | 5/1.2               | 1          |          |              |

| T10,T11     | 15/1.2              | 3          |          |              |

| T12, T13    | 15/1.2              | 1          |          |              |

In Table 3.2 the transistor size of Tbias and T3 ensure that the current present at the bias transistor, within margins, is translated to the drain current of T3 without scaling.

# 3.3 Diode-Load Differential Amplifier

As discussed in Chapter 2, resistive loads can be replaced by diode-connected transistors. While this approach offers certain advantages, such as improved matching and area efficiency, it also has some design trade-offs. One of these trade-offs is the maximum allowable common-mode voltage, which in turn limits the overall output voltage swing. An example of a differential amplifier using diode-loads is illustrated in Figure 3.2.

Figure 3.2: Three Stage Diode-Load Differential Amplifier

In Figure 3.2, a supply voltage of 5 V is used with a 21 µA biasing current. As explained before, the voltage drop is now created by a diode-connected transistor and not a resistive load. Although this circuit shares structural similarities with the previously discussed topology, it introduces several differences. One of the added elements is feedback by capacitive and resistive components. This technique, commonly referred to as Miller compensation, plays a role in increasing the stability of a system by shifting the dominant and non-dominant poles to a lower and higher frequency, respectively [53],[54]. A second key difference is the removal of the source-follower stage and the addition of a buffer stage at the output to ensure reliable signal transfer. To scale the different transistors, the transfer function is calculated with the transconductance of the different devices, which is shown in Appendix B. The different parameters for the components used in this circuit are presented in Table 3.3.

| Table 3.3: | Diode-Load | Differential | Amplifier | Sizes | and | Values |

|------------|------------|--------------|-----------|-------|-----|--------|

|            |            |              |           |       |     |        |

| Transistor | $W/L (\mu m/\mu m)$ | multiplier | Resistor  | $R(k\Omega)$ |

|------------|---------------------|------------|-----------|--------------|

| T1,T2      | 200/1.2             | 4          | R1, R2    | 70           |

| T3,Tbias   | 180/1.2             | 7          | Capacitor | C (pF)       |

| T5,T4      | 1/1                 | 1          | C1,C2     | 8            |

| T6,T7      | 80/1.2              | 1          |           |              |

| T8,T9      | 11.1/1.2            | 2          |           |              |

| T10, T11   | 70.8/1.2            | 8          |           |              |

| T12, T13   | 20/0.9              | 4          |           |              |

| T14, T15   | 40/1.2              | 2          |           |              |

| T16, T17   | 20/1.2              | 2          |           |              |

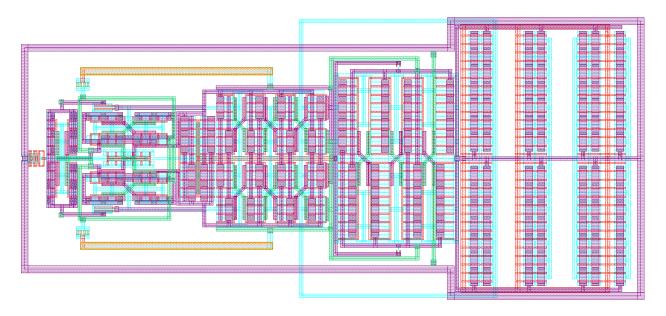

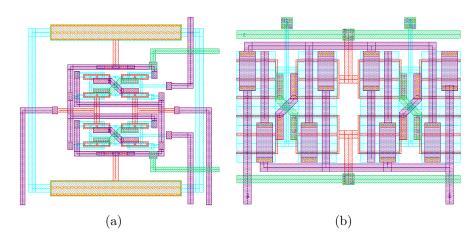

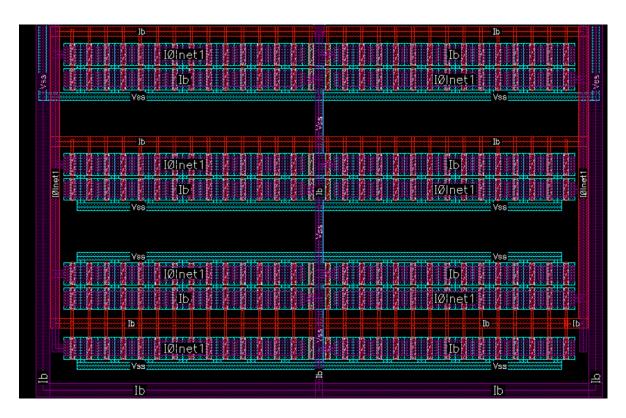

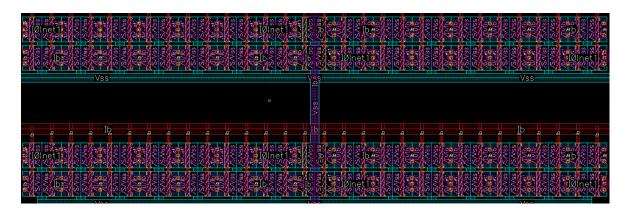

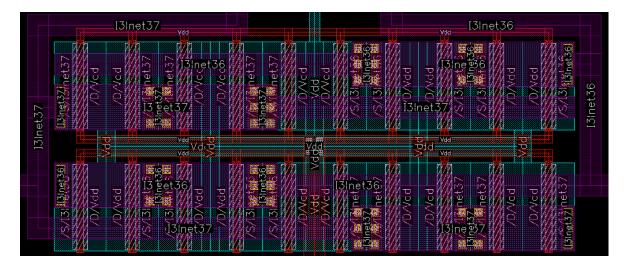

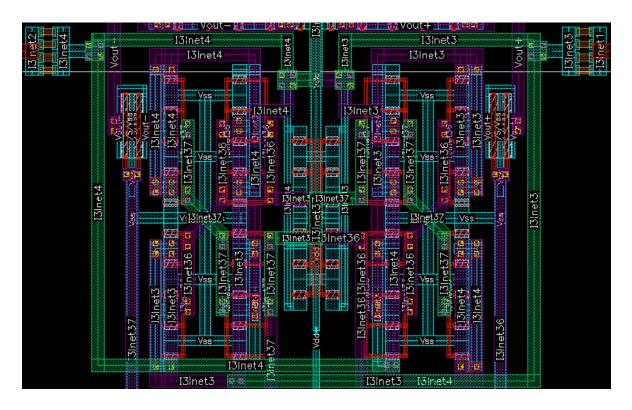

For this circuit a layout is created using the PragmatIC Semiconductors 600nm technology node [55]. The resulting layout is illustrates in Figure 3.3. As previously discussed in the schematic analyses, the layout can be divided into three distinct substage, corresponding to the functional blocks of the amplifier.

Figure 3.3: Diode-Load Differential Amplifier Layout

A more detailed representation of the layout is provided in Appendix A. The designed circuit employs a common-centroid layout technique, minimizing mismatch by ensuring that transistors operating in complementary roles are equally affected by coupling from aggressor signals [56],[57]. This layout strategy is evident in Figure A.4, where metal layers 1 and 2 are crossed to ensure connection between the different transistor stacks. To mitigate the impact of mechanical stress induced by overlying metal layers, these are extended across adjacent transistors to ensure uniform stress distribution. Metal layer 1 is primarily used to route signals within individual amplification stages. In the third amplification stage, diode-connected transistors are positioned between the input transistors to reduce layout area, as illustrated in Figure A.7.

# 3.4 Bootstrapped Differential Amplifier

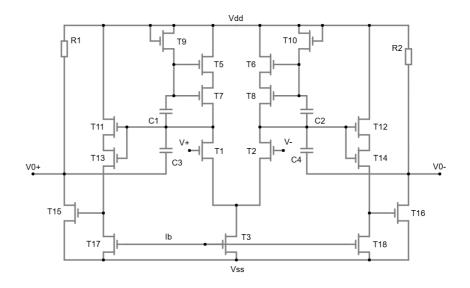

The bootstrapping circuit is created out of two stages. The fundamental principle underlying bootstrapping is discussed in Chapter 2. By employing a feedback mechanism, it can assure, within certain limits, that the voltage present at the gate of a transistor is a predetermined amount greater then that of the source. This results in a constant gate-source voltage difference  $\Delta V_{gs}$ , which in turn stabilizes the drain current  $I_d$ . The implementation of a bootstrapping circuit in a differential amplifier is illustrated in Figure 3.4, whilst Table 3.4 shows the different values for the used transistors, capacitors and resistors.

Figure 3.4: Two Stage Bootstrapped Differential Amplifier

| Table 3.4: Bootstrapped Differential Amp | oliner Sizes | and Values |

|------------------------------------------|--------------|------------|

|------------------------------------------|--------------|------------|

| Transistor      | W/L (μm/μm) | multiplier | Resistor  | $R(k\Omega)$ |

|-----------------|-------------|------------|-----------|--------------|

| T1,T2           | 30/1.2      | 4          | R1, R2    | 100          |

| Т3              | 180/1.2     | 7          | Capacitor | C (F)        |

| Tbias           | 60/1.2      | 7          | C1,C2     | 800µ         |

| T5,T6,T7,T8     | 1/1.2       | 2          | C3,C4     | 10p          |

| T9,T10          | 20/0.6      | 1          |           |              |

| T11,T13,T12,T14 | 1.5/0.6     | 2          |           |              |

| T17, T18        | 60/1.2      | 7          |           |              |

| T15, T16        | 15/1.2      | 25         |           |              |

The circuit illustrated in Figure 3.4 operates with a 3 V power supply and 1 µA biasing current. Transistors T1 to T3 form a differential pair configuration, as previously described. In this implementation, the traditional resistive loads are replaced with a bootstrapping circuit, which is represented by transistors T5 to T10 and capacitors C1 and C2. Transistors T7 and T8 function as cascoded devices, ensuring a lower common-mode voltage at the output of the differential stage. Transistors T9 and T10 are diode-connected to prevent current flow towards the power supply rail. Following the first stage, a level shifter circuit is employed to further lower the common-mode voltage, ensuring that transistors T15 and T16 remain in saturation region during operation. Capacitor C3 and C4 are used as Miller compensation, which is discussed before.

As shown in Table 3.4, transistor Tbias is sized to be three times smaller than T3. This sizing results in a biasing current that is approximately one-third of the current flowing through the differential pair, thereby contributing to a reduced overall power consumption in the circuit.

# 3.5 Transconductance Boosting Differential Amplifier

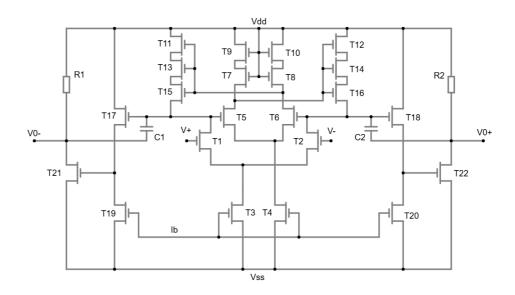

The final implemented circuit employs a feedback mechanism to enhance the transconductance of specific transistors. This technique, known as transconductance boosting, is similar to bootstrapping in that it stabilizes the current through the load of the differential pair. As a result, the load node presents a higher effective impedance, thereby improving the overall gain of the amplifier. In bootstrapping the feedback is of the capacitive kind, whilst in the Transconductance boosting a source sensing differential pair is used which increases the gate voltage relative to the source voltage, ensuring that  $V_{qs}$  of a transistor is stable [44], [58], [59].

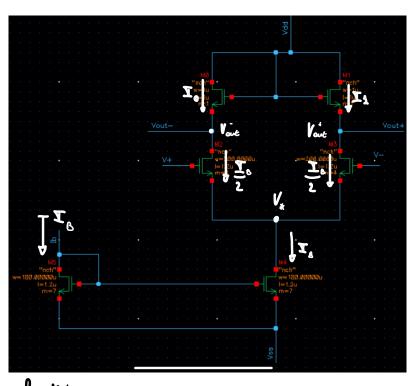

Figure 3.5: Two Stage Transconductance Boosting Differential Amplifier

The circuit in Figure 3.5 is implemented using a 3 V power supply and 1 µA biasing current. It uses two current reference transistors, T3 and T4, which are utilized to bias two separate differential pairs. One differential pair, with transistors T5 and T6, is responsible for sensing the source voltage of the load transistors T11 to T16. Transistors T1 and T2 operate as a conventional differential pair with their output connected to a source-follower and an additional amplification stage. The different used component values can be found in Table 3.5.

| Thomaiston                     | W/T (was /was)      | manitimii an | Dogiston  | D (1-0)      |

|--------------------------------|---------------------|--------------|-----------|--------------|

| Transistor                     | $W/L (\mu m/\mu m)$ | multiplier   | Resistor  | $R(k\Omega)$ |

| T1, T2                         | 24/0.6              | 3            | R1, R2    | 180          |

| T3, Tbias                      | 6/1.2               | 2            | Capacitor | C (pF)       |

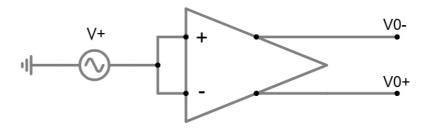

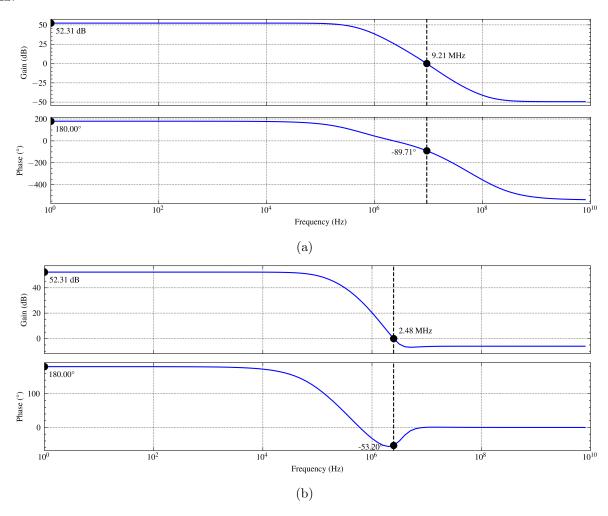

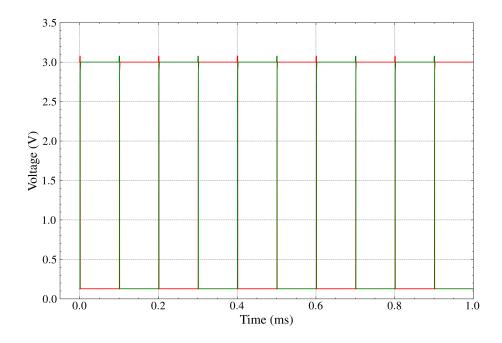

| T4                             | 3/1.2               | 1            | C1,C2     | 5            |