# Faculteit Industriële Ingenieurswetenschappen

master in de industriële wetenschappen: elektronica-

### **Masterthesis**

The Development of an Analog Front End in LTPO Technology

#### **Biorn Spauwen**

Scriptie ingediend tot het behalen van de graad van master in de industriële wetenschappen: elektronica-ICT

### **PROMOTOR:**

Prof. dr. ing. Kris MYNY

#### **PROMOTOR:**

dr. ir. Mohit DANDEKAR

#### **BEGELEIDER:**

De heer Yari NOWICKI

Gezamenlijke opleiding UHasselt en KU Leuven

Universiteit Hasselt | Campus Diepenbeek | Faculteit Industriële Ingenieurswetenschappen | Agoralaan Gebouw H - Gebouw B | BE 3590 Diepenbeek

Universiteit Hasselt | Campus Diepenbeek | Agoralaan Gebouw D | BE 3590 Diepenbeek Universiteit Hasselt | Campus Hasselt | Martelarenlaan 42 | BE 3500 Hasselt

$\frac{2024}{2025}$

# Faculteit Industriële Ingenieurswetenschappen

master in de industriële wetenschappen: elektronica-ICT

### **Masterthesis**

### The Development of an Analog Front End in LTPO Technology

#### **Bjorn Spauwen**

Scriptie ingediend tot het behalen van de graad van master in de industriële wetenschappen: elektronica-ICT

#### **PROMOTOR:**

Prof. dr. ing. Kris MYNY

#### **PROMOTOR:**

dr. ir. Mohit DANDEKAR

#### **BEGELEIDER:**

De heer Yari NOWICKI

## **Preface**

The conclusion of this master's thesis marks the end of my four-year studies at the Faculty of Engineering Technology of Hasselt University and KULeuven. I am leaving this period of my life behind not only with an engineering master's degree but also with many fond memories and personal growth. The writing of this thesis has taught me many new things about the link between electrical circuit design and healthcare, which will greatly help me towards my future career goals.

Firstly, I would like to show my gratitude to my co-advisor at ES&S ing. Yari Nowicki, for his guidance through this thesis. I would also like to thank Prof. dr. ing. Kris Myny for his unwavering commitment towards the Master's programme Electronics-ICT and its students. In addition, I would like to thank ing. Jelle Biesmans and Muhammad Dawood Asghar for their support.

Secondly, I would like to thank my family for always standing alongside me and providing a listening ear through the most stressful moments.

And finally, I would like to thank my peers and friends for their constant companionship and a healthy sense of competition that has kept me pushing to get the best version out of myself.

# Contents

| t of tables t of figures t of abbreviations                                                                                                                                                                                                       | 8                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                   | 8                                                                                                                                                                                                                         |

| t of abbreviations                                                                                                                                                                                                                                |                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                   | ç                                                                                                                                                                                                                         |

| stract                                                                                                                                                                                                                                            | 11                                                                                                                                                                                                                        |

| stract in Dutch                                                                                                                                                                                                                                   | 13                                                                                                                                                                                                                        |

| 1.1 Motivation                                                                                                                                                                                                                                    | 15<br>16                                                                                                                                                                                                                  |

| 2.1 Thin Film Transistors (TFTs)  2.2 LTPO Fabrication and Applications  2.2.1 Fabrication Process  2.2.2 Pixel Circuit  2.2.3 Full Adder ALU  2.2.4 Operational Amplifier  2.3 AFE for ECG signals  2.3.1 Measurement  2.3.2 Amplification Stage | 18<br>18<br>18<br>19<br>20<br>20<br>21                                                                                                                                                                                    |

| 3.1 Fully Differential and Single-Ended amplifiers 3.2 Input differential pair                                                                                                                                                                    | 25<br>27<br>28<br>29<br>30                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                   | 2.2.2       Pixel Circuit          2.2.3       Full Adder ALU          2.2.4       Operational Amplifier          2.3       AFE for ECG signals          2.3.1       Measurement          2.3.2       Amplification Stage |

|    | 3.8<br>3.9               | Two-Stage Amplifier                         | 31<br>33  |  |  |  |

|----|--------------------------|---------------------------------------------|-----------|--|--|--|

| 4  | Results and Discussion 3 |                                             |           |  |  |  |

|    | 4.1                      | Simulation Models                           | 35        |  |  |  |

|    | 4.2                      | Simulation Setup                            | 35        |  |  |  |

|    | 4.3                      | Simple Two-Stage amplifier                  | 36        |  |  |  |

|    |                          | 4.3.1 Circuit Design                        | 36        |  |  |  |

|    |                          | 4.3.2 Test Bench and Simulation Results     | 37        |  |  |  |

|    |                          | 4.3.3 Discussion                            | 40        |  |  |  |

|    | 4.4                      | Current Mirror Based Amplifier              | 40        |  |  |  |

|    |                          | 4.4.1 Circuit Design                        | 40        |  |  |  |

|    |                          | 4.4.2 Test Bench and Simulation Results     | 41        |  |  |  |

|    |                          | 4.4.3 Discussion                            | 41        |  |  |  |

|    | 4.5                      | High Gain Two Stage Amplifier               | 44        |  |  |  |

|    |                          | 4.5.1 Circuit Design                        | 44        |  |  |  |

|    |                          | 4.5.2 Test Bench and Simulation Results     | 44        |  |  |  |

|    |                          | 4.5.3 Discussion                            | 46        |  |  |  |

|    | 4.6                      | Digital Signal Processing Unit              | 49        |  |  |  |

|    |                          | 4.6.1 StrongARM Latch                       | 50        |  |  |  |

|    |                          | 4.6.2 Edge detection                        | 51        |  |  |  |

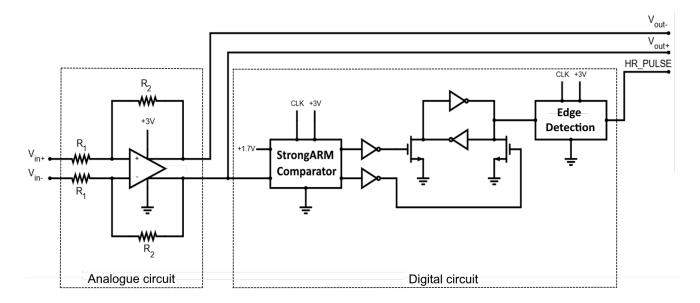

|    | 4.7                      | Complete AFE                                | 51        |  |  |  |

|    |                          | 4.7.1 Circuit                               | 51        |  |  |  |

|    |                          | 4.7.2 Clock Frequency and Power Consumption | 53        |  |  |  |

|    | 4.8                      | Comparison to Other Work                    | 54        |  |  |  |

| 5  | Con                      | nclusion                                    | <b>57</b> |  |  |  |

|    | 5.1                      | Conclusion                                  | 57        |  |  |  |

|    | 5.2                      | Improvements                                | 58        |  |  |  |

|    | 5.3                      | Future Work                                 | 58        |  |  |  |

| Ac | knov                     | wledgements                                 | <b>59</b> |  |  |  |

| Bi | bliog                    | graphy                                      | 65        |  |  |  |

| Aı | open                     | dix                                         | 67        |  |  |  |

# List of Tables

| 4.1 | TFT dimensions and bias parameters of the amplifier of the two stage amplifier | 37 |

|-----|--------------------------------------------------------------------------------|----|

| 4.2 | Performance parameters of the two stage amplifier                              | 39 |

| 4.3 | TFT dimension and bias parameters of the current mirror amplifier              | 43 |

| 4.4 | Performance parameters of the current mirror amplifier                         | 44 |

| 4.5 | TFT dimension and bias parameters of the current mirror amplifier              | 45 |

| 4.6 | Performance parameters of the high gain two stage amplifier                    | 46 |

| 4.7 | Comparison of this work with other state-of-the-art TFT amplifiers             | 56 |

# List of Figures

| 2.1  | Typical device configuration of LTPO                                                                                             | 18 |

|------|----------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | LTPO pixel circuit schematic                                                                                                     | 19 |

| 2.3  | Circuit diagram of 1-bit LTPO ALU                                                                                                | 19 |

| 2.4  | Schematic of the proposed two-stage LTPO op-amp, with the W/L ratio of each                                                      |    |

|      | TFT in $\mu m.$                                                                                                                  | 20 |

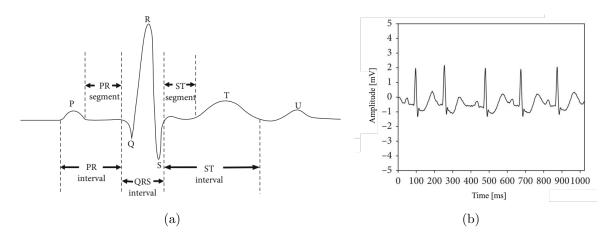

| 2.5  | Typical ECG signal cycle with a) a single ECG cycle, and b) ECG over a 10-second period                                          | 21 |

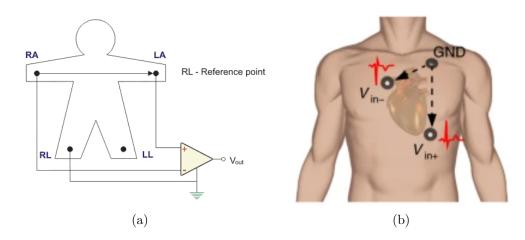

| 2.6  | Illustrations for the electrical signal of Lead I measurement and the placement of the electrodes in context for a smart plaster | 22 |

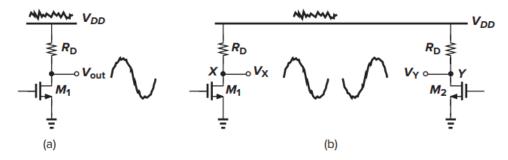

| 3.1  | Effect of supply noise on (a) a single-ended circuit and (b) a differential circuit.  .                                          | 26 |

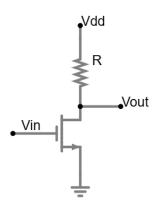

| 3.2  | Common-source input pair                                                                                                         | 26 |

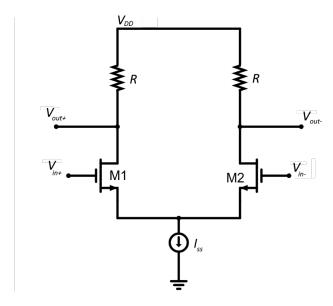

| 3.3  | Input differential pair with resistive load                                                                                      | 27 |

| 3.4  | Differential pair circuit with p-type load                                                                                       | 28 |

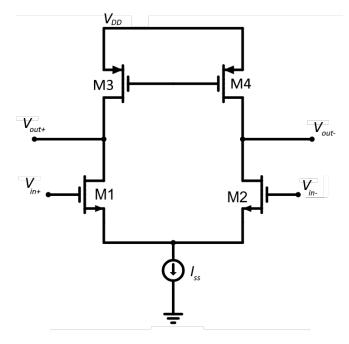

| 3.5  | Slew rate example                                                                                                                | 29 |

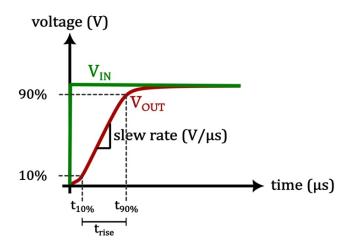

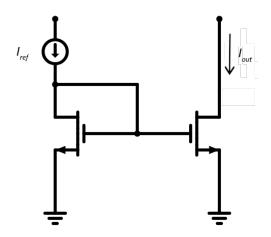

| 3.6  | Simple NMOS current mirror                                                                                                       | 30 |

| 3.7  | Common source stage with a cascode transistor                                                                                    | 32 |

| 3.8  | Typical two stage amplifier circuit                                                                                              | 32 |

| 4.1  | Two-stage amplifier in LTPO                                                                                                      | 36 |

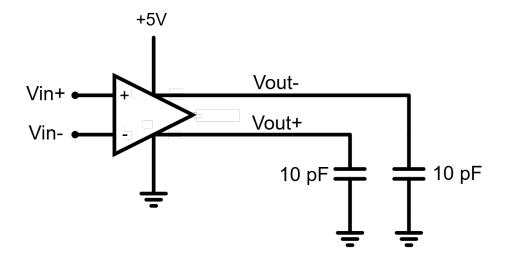

| 4.2  | Open loop test bench used for the two stage amplifier                                                                            | 37 |

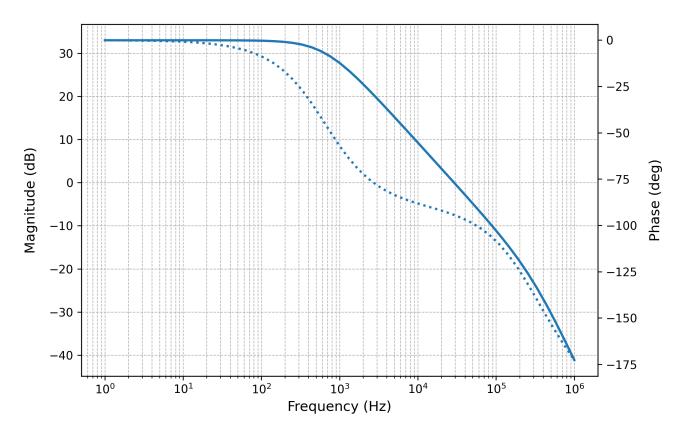

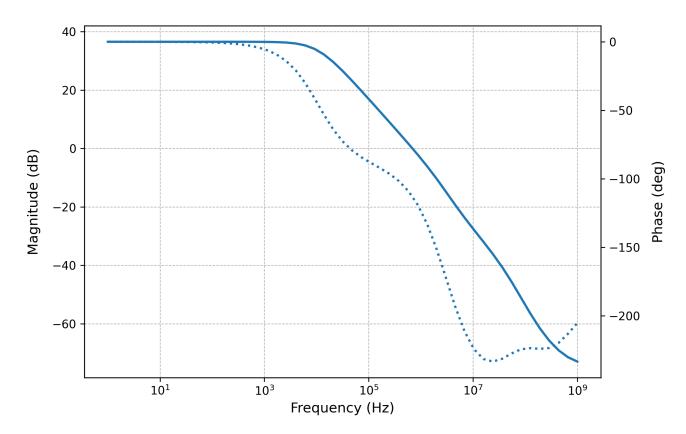

| 4.3  | Bode plot of the open loop gain (solid line) and phase delay (dotted line) of the two stage amplifier                            | 38 |

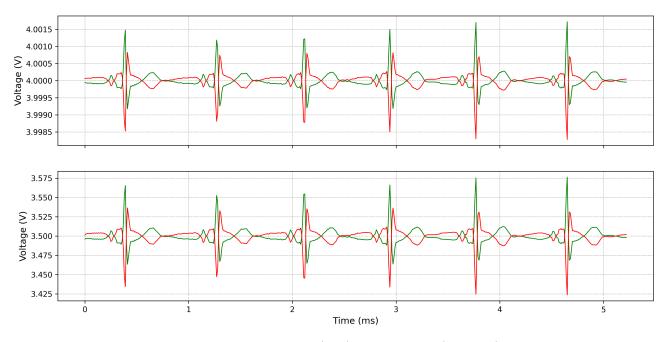

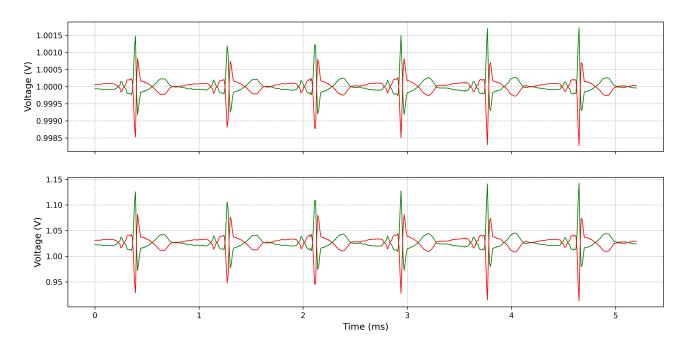

| 4.4  | Transient response of the input (top) and output (bottom) signal of the two stage                                                |    |

|      | amplifier, with the positive nodes in green and negative nodes in red                                                            | 38 |

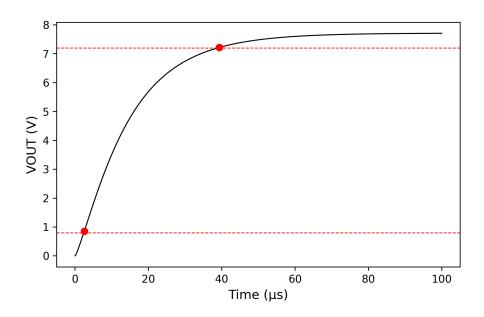

| 4.5  | Slew rate of the two stage amplifier                                                                                             | 39 |

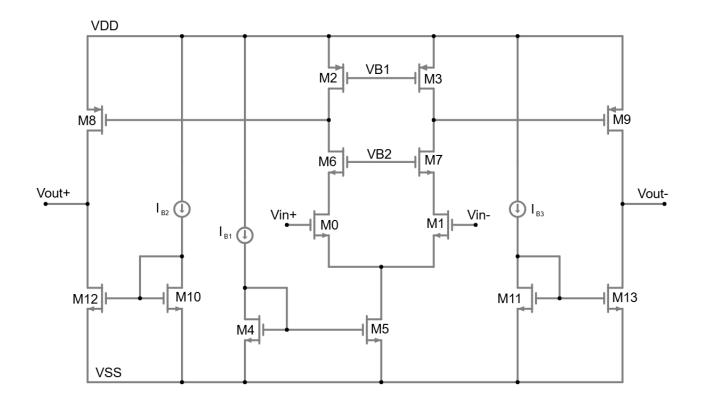

| 4.6  | Circuit diagram of a current mirror based amplifier                                                                              | 41 |

| 4.7  | Open loop test bench of the current mirror amplifier                                                                             | 42 |

| 4.8  | Bode plot of the open loop gain (solid line) and phase delay (dotted line) of the                                                |    |

|      | current mirror amplifier                                                                                                         | 42 |

| 4.9  | Transient response of the input (top) and output (bottom) signal of the current                                                  |    |

|      | mirror amplifier, with the positive nodes in green and negative nodes in red. $$                                                 | 43 |

|      | Circuit diagram the high gain two stage amplifier                                                                                | 45 |

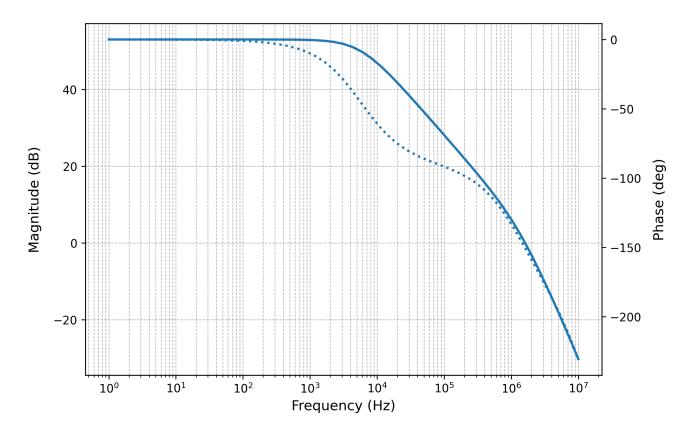

| 4.11 | Bode plot of the open loop gain (solid line) and phase delay (dotted line) of the                                                |    |

|      | high gain two stage amplifier                                                                                                    | 46 |

| 4.12 | Transient response of the input and output (top) and output (bottom) signal of               |    |

|------|----------------------------------------------------------------------------------------------|----|

|      | the high gain two stage amplifier, with the positive nodes in green and negative             |    |

|      | nodes in red                                                                                 | 47 |

| 4.13 | Test bench for the high gain two stage amplifier with negative feedback                      | 47 |

| 4.14 | Bode plot of the closed loop gain (solid line) and phase delay (dotted line) of the          |    |

|      | high gain two stage amplifier                                                                | 48 |

| 4.15 | Slew rate simulation of the high gain two stage amplifier                                    | 48 |

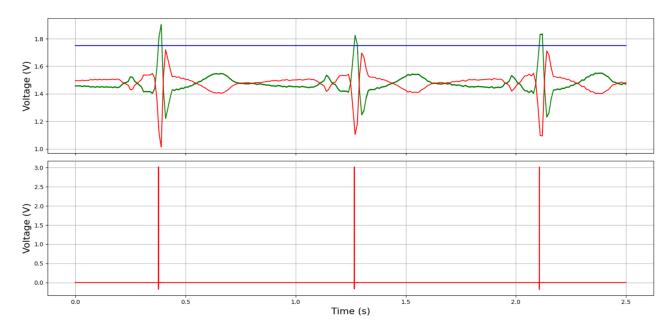

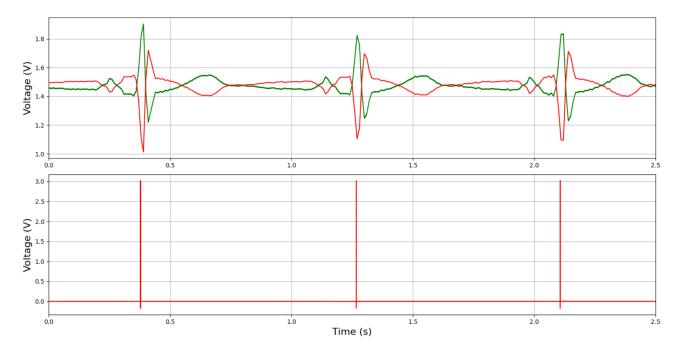

| 4.16 | Output voltage signals of the AFE. Top: positive (green) and negative (red) output           |    |

|      | voltages, and the reference voltage (blue). Bottom: digital heartbeat pulse                  | 49 |

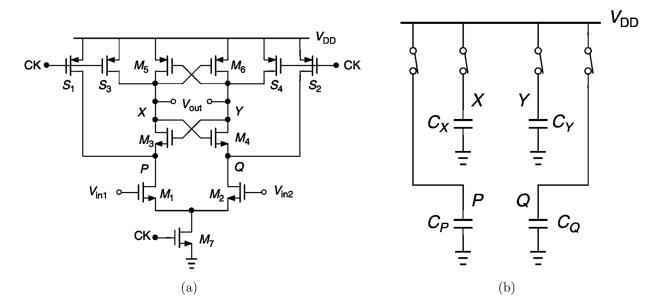

| 4.17 | StrongARM latch a) circuit and b) its equivalent circuit in the reset stage                  | 50 |

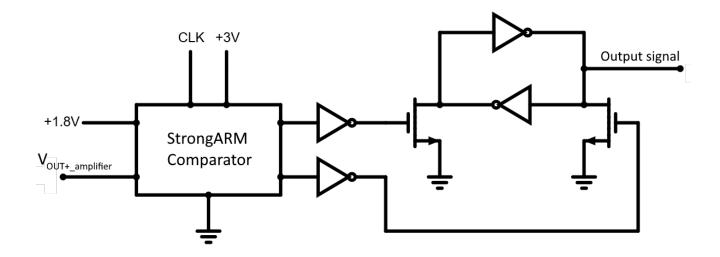

| 4.18 | The StrongARM latch followed by the SR latch                                                 | 51 |

| 4.19 | Output signals of the AFE during heartbeat detection. Top: positive (green) and              |    |

|      | negative (red) input voltages of the comparator and its reference voltage (blue).            |    |

|      | Middle: output of the StrongARM comparator. Bottom: output signal after the                  |    |

|      | SR latch                                                                                     | 52 |

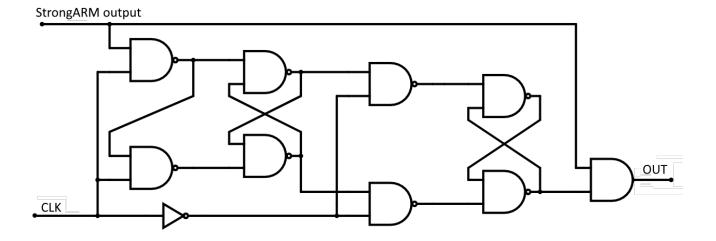

| 4.20 | Edge detector circuit                                                                        | 52 |

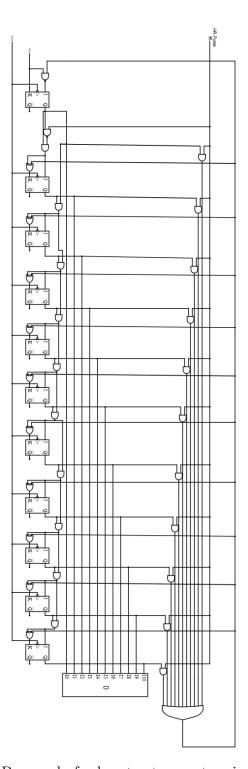

| 4.21 | Full circuit diagram of the AFE                                                              | 53 |

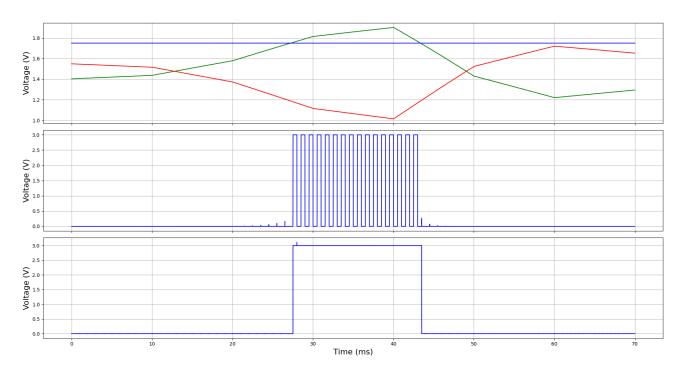

| 4.22 | Output signals of the AFE. Top: $V_{out+}$ and $V_{out-}$ . Bottom: Digital heartbeat pulse. | 54 |

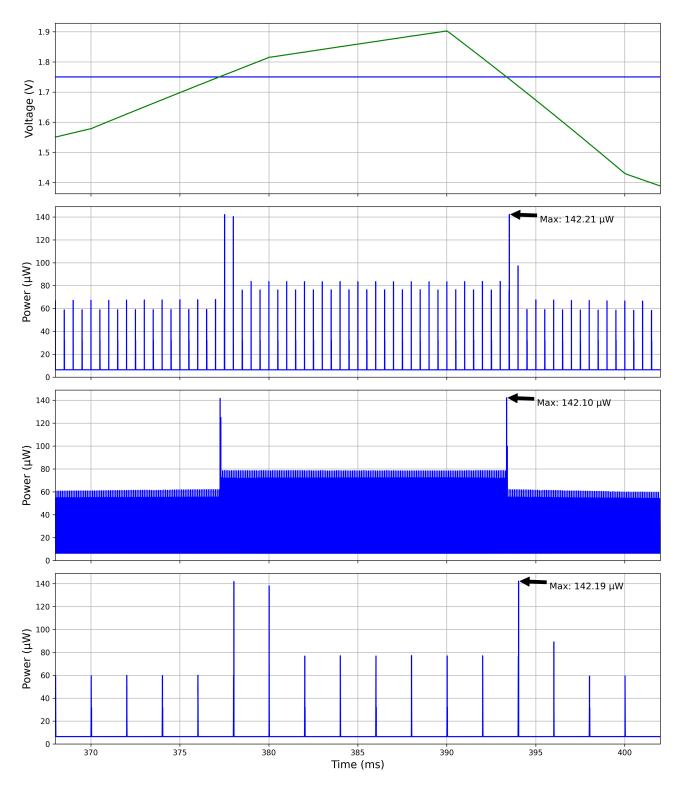

| 4.23 | Top plot: ECG signal around the R-wave region and a 1.75 V reference voltage.                |    |

|      | Second plot: Power consumption measured with a 1 kHz clock frequency. Third                  |    |

|      | plot: Power consumption measured with a 10 kHz clock frequency. Fourth plot:                 |    |

|      | Power consumption measured with a 250 Hz clock frequency                                     | 55 |

| 5.1  | Proposal of a heart rate counter circuit in LTPO                                             | 67 |

# List of Abbreviations

| a-IGZO | amorphous Gallium-Indium-Zinc-Oxide               |

|--------|---------------------------------------------------|

| AC     | Alternating Current                               |

| ADC    | Analogue to Digital Converter                     |

| AFE    | Analogue Front-End                                |

| ALU    | Arithmetic Logic Unit                             |

| CLK    | Clock                                             |

| CMRR   | Common Mode Rejection Ratio                       |

| DC     | Direct Current                                    |

| DSP    | Digital Signal Processing                         |

| ECG    | Electrocardiogram                                 |

| HRV    | Heart Rate Varation                               |

| LTPO   | Low-Temperature Poly Oxide                        |

| LTPS   | Low-Temperature Poly Silicon                      |

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor |

| SR     | Slew Rate                                         |

| TFT    | Thin Film Transistor                              |

| VDD    | Positive supply voltage                           |

| Vin    | Input voltage                                     |

| Vout   | Output voltage                                    |

| VSS    | Negative supply voltage                           |

| W/L    | Width to Length Ratio                             |

## Abstract

Thin-film transistors (TFTs) have gained increasing interest in specific applications due to their ability to bend and fold in any direction. One promising application is electrocardiogram (ECG) signal monitoring, where flexible chips could enable on-skin amplification and local processing of the heart's signals. A recent advancement in TFT technology is the emergence of Low-Temperature Polycrystalline Oxide (LTPO), which hybridises the p-type TFTs of Low-Temperature Poly Silicon and the n-type TFTs from Amorphous Indium Gallium Zinc Oxide. In this thesis, an analogue front end (AFE) for ECG is developed using LTPO technology. The AFE consists of an analogue amplifier, followed by a digital heartrate detection circuit.

The amplifier employs a two-stage fully differential architecture featuring cascaded transistors. The design achieves a closed-loop gain of 49.6 dB ( $\approx 300 x$ ), with a -3 dB cut-off frequency of 8.5 kHz and a phase margin of 30°. This combination of high gain and appropriate bandwidth makes the amplifier suitable for ECG monitoring. Additionally, a digital heartbeat detector is designed based on the StrongARM latch topology, followed by an edge detector. The complete AFE provides three outputs: two amplified differential output signals and a digital heartbeat pulse. The system operates on a 3 V power supply, with an average power consumption of 6.8  $\mu$ W. The results show significant improvement, especially in power consumption, compared to previous LTPO research.

## Abstract in Dutch

Thin Film Transistors (TFT's) staan bekend om hun buigbaarheid in alle richtingen, wat hen bijzonder geschikt maakt voor flexibele toepassingen. Een interessante toepassing is het lokaal monitoren van elektrocardiografische (ECG) signalen, waarbij een volledig flexibele chip de elektrische hartsignalen ter plaatse kan versterken en verwerken. Een recente ontwikkeling in TFT-technologie is de opkomst van Low Temperature Polycrystalline Oxide (LTPO), dat een hybride is van de p-type TFT's van Low Temperature Poly Silicon en de n-type TFT's van Amorf Indium Gallium Zinc Oxide. In deze thesis werd een analoge front end (AFE) in LTPO ontworpen, specifiek voor ECG, bestaande uit een analoge signaalversterker en een digitaal hartslagdetectiecircuit.

De signaalversterker bestaat uit een tweetraps volledig differentiële architectuur met in cascade geschakelde transistors. Het ontwerp bereikt een geslotenlusversterking van 49,6 dB ( $\approx 300 x$ ), met een -3 dB afsnijfrequentie van 8.5 kHz en een fasemarge van 30°, wat het geschikt maakt voor nauwkeurige ECG-verwerking. Daarnaast is er een digitale hartslagdetector ontworpen op basis van de StrongARM-latchtopologie, gevolgd door een flankdetector. De complete AFE levert drie uitgangen: twee versterkte differentiële uitgangssignalen en een digitale hartslagpuls. Het systeem werkt op een voeding van 3 V, met een gemiddeld stroomverbruik van 6,8  $\mu$ W. Vergeleken met eerder LTPO-onderzoek tonen de resultaten een aanzienlijke verbetering, vooral in stroomverbruik.

## Chapter 1

## Introduction

### 1.1 Motivation

In the analogue circuit design sector, thin-film transistors (TFTs) are emerging as a complementary technology to the industry-standard silicon-based Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) technologies in specific applications because of their ability to fold and bend in any direction. TFTs are already widely used in displays on mobile devices, alongside some promising applications in other fields such as wearable healthcare devices [1], [2], [3], [4].

Recently, a new TFT technology has surfaced that hybridises the p-type TFTs of Low-Temperature Poly Silicon (LTPS) and the n-type TFTs from Amorphous Indium Gallium Zinc Oxide (a-IGZO), called Low-Temperature Polycrystalline Oxide (LTPO). This technology has found its use in high-end variable refresh rate displays [5], [6]. However, their integration into non-display analogue circuits remains largely unexplored. This thesis aims to develop an application for LTPO TFT technology, to be used in a low-power analogue front-end (AFE) circuit for electrocardiogram (ECG) signal measurement, thereby extending its application beyond conventional display use. Ultra-thin chips and sensors that can bend in any direction have a high potential as wearable health monitors [7]. A device like this can potentially be attached to the human skin like a plaster, unlocking the ability to passively monitor the patient's health in new ways without the presence of a qualified physician. To make such technology practical and accessible, it is crucial that these systems are both low-power and cost-effective. Minimising power consumption enables long-term continuous monitoring without frequent battery replacements or recharging, which is essential for real-world medical use. Likewise, keeping production costs low enables widespread deployment in both hospitals and home environments, helping to make healthcare more accessible and scalable.

### 1.2 Problem Statement

During a standard ECG measurement, electrodes are attached directly to the skin to record the electrical activity of the heart in a technique called analogue lead derivation (ALD) [8]. These analogue signals are then fed into an analogue-to-digital converter (ADC), or directly transferred via long cables to a processing unit for further analysis. In this latter configuration, weak ECG signals are susceptible to noise generated by external factors like the human body, electronic

equipment, or cables. This significantly reduces the integrity of very the low-power biological signals [9]. However, if the amplifier/AFE is connected directly to the electrodes on the skin, which are extremely close to the source of the signals, then the noise can easily be subtracted. This ensures that only the essential components of the ECG are transmitted with high signal integrity [10]. A typical AFE contains more than just an amplifier. It usually consists of a variety of components, such as operational amplifiers, active filters, and analogue to digital converters (ADCs) [11].

## 1.3 Objectives

The primary objective of this thesis is to explore the application potential of LTPO TFT technology and to evaluate its performance in comparison with other TFT technologies.

The research first focusses on the design of an analogue signal amplifier tailored for ECG signals. Given the characteristics of ECG waveforms, the amplifier will be optimised to deliver high gain at low frequencies while consuming minimal power, maintaining excellent signal integrity, and to drive large loads at the output without degradation in performance.

The second objective is to develop a digital signal processing (DSP) unit capable of receiving the amplified analogue signals, accurately detecting heartbeat events, and generating corresponding digital outputs for further analysis. This unit will be designed with an emphasis on low power consumption, making it suitable for continuous operation in wearable devices.

Together, these objectives aim to provide new research towards LTPO as a viable option in TFT technologies for integration in fully flexible and wearable devices, with a specific application in the healthcare sector.

## 1.4 Thesis outline

The rest of this thesis is divided into four more chapters:

- Chapter 2 Literature Study: Covers the fundamentals of LTPO TFT technology, ECG signal characteristics, and existing analogue front-end designs.

- Chapter 3 Analogue Design Methodology: Describes the design approach for the analogue amplifier, and the considerations made.

- Chapter 4 Results and Discussion: Presents the design, simulation results, and performance analysis of three proposed ECG amplifiers, and the digital signal processing unit. Additionally, a power consumption analysis is made on the complete AFE circuit and comparisons are made to other state-of-the-art TFT designs.

- Chapter 5 Conclusion and Discussion: Concludes the results of the thesis and suggests improvements and future follow-up work on this thesis.

## Chapter 2

## Literature study

## 2.1 Thin Film Transistors (TFTs)

TFTs are a type of Field Effect Transistor (FET) based on the deposition of thin layers of semiconductor, dielectric, and metallic contacts on an insulating substrate. Compared to the more commonly known Metal-Oxide-Semiconductor Field Effect Transistors (MOSFETs), TFTs are typically manufactured on top of a glass or plastic substrate in a relatively low-temperature process, allowing for extremely thin and flexible electronic applications. In addition, TFTs are cheap and easy to manufacture on a large scale [12]. So far, TFTs have mostly found their use in active matrix displays such as Liquid Crystal Displays (LCDs) [13] as on/off switches for all individual pixels and drivers in flat-panel displays due to their fast switching ability [14]. TFT is a collective name for multiple structure designs. Some of the most relevant are the following:

- Amorphous silicon (a-Si)

- Amorphous indium gallium zinc oxide (a-IGZO)

- Low temperature poly silicon (LTPS)

- Low temperature poly oxide (LTPO)

The most commonly used TFT in LCD displays is a-Si due to its simplicity and cheap manufacturing. However, its relatively low carrier mobility means slower switching. More high-end applications are therefore opting for different materials, such as a-IGZO or LTPS. LTPS TFTs, for example, achieve a much higher field-effect mobility ( $\mu_{\rm FE}$ ) of approximately 100 cm<sup>2</sup>/Vs compared to 1 cm<sup>2</sup>/Vs for a-Si [15], [16]. However, LTPS technology is less suitable for lower frame rate displays due to its relatively high off-state currents ( $I_{\rm FE}$ ) [17]. In contrast, a-IGZO TFTs exhibit significantly lower leakage currents, making them much better suited for such applications. Nevertheless, their  $\mu_{\rm FE}$  of approximately 10 cm<sup>2</sup>/Vs is comparatively lower and therefore less desirable for high-performance circuits. However, a-IGZO consists only of n-type transistors (contrary to the usual CMOS transistor topology, consisting of both n-type and p-type transistors) due to the high density of defect states above the valence band [18], [19]. To overcome the limitations of both technologies, LTPO was developed as a hybrid circuit architecture that combines p-type LTPS TFTs for driving elements with n-type a-IGZO TFTs for switching elements. This enables the implementation of complementary CMOS-like logic, offering advantages such as rail-to-rail output, reduced noise, and lower power consumption.

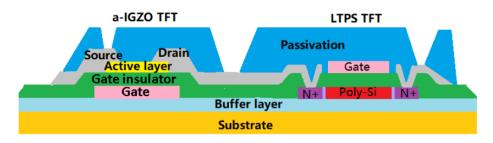

Figure 2.1: Typical device configuration of LTPO [21].

## 2.2 LTPO Fabrication and Applications

In 2017, the first hybrid integration of p-channel LTPS and n-channel a-IGZO on the same substrate was demonstrated [20]. Since then, LTPO has been commercially implemented primarily in variable refresh rate displays [5]. This section will go over the fabrication process of LTPO and explores and compares several other research efforts involving LTPO technology.

### 2.2.1 Fabrication Process

The typical cross-sectional structure of an LTPO inverter is illustrated in Figure 2.1 with the n-type a-IGZO TFT on the left and the p-type LTPS TFT on the right. The fabrication is done by building the p-channel TFTs in a top-gate, top-contact configuration, followed by the n-type TFT in a bottom-gate, top-contact configuration. First, the process starts by depositing a thick SiO<sub>2</sub> layer onto a substrate via plasma enhanced chemical vapour deposition (PECVD). The Poly-Si layer is grown by consequently treating an a-Si film placed on the buffer layer via PECVD. This newly formed Poly-Si layer is then photolithographically patterned and then etched via reactive ion etching (RIE) to form the isolated islands. The N+ source and drain regions are doped with boron ion implantation and followed up by a rapid thermal annealing (RTA) process. Both the n-type and the p-type gate are placed by direct current sputtering and wet etching of the metal oxide layer. The gate insulator layer also serves as an interlayer on the LTPS TFT between the gate and the Poly-Si layer and consists of another SiO<sub>2</sub> layer placed via PECVD. Note that source and drain contact holes are also formed in this stage by patterning. Next, the n-type a-IGZO active layer is deposited by reactive sputtering and placed with wet etching. The source and drain metal layers are formed by sputtering and patterning another metal oxide layer. As the last step, a thick passivation layer is deposited by PECVD, and via holes are formed at the source and drain. A more elaborate explanation of the fabrication process can be found in [13], [20], [17].

### 2.2.2 Pixel Circuit

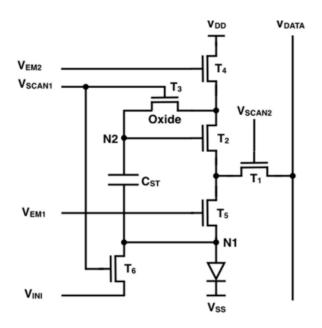

The first commercial implementation of LTPO TFTs on the market was in the Apple Watch Series 4. Figure 2.2 represents the circuit that drives each pixel on the AMOLED screen. The circuit consists of one metal oxide (a-IGZO) TFT used as the switching transistor, five LTPS TFTs, and a storage capacitor. Using a-IGZO as the driving transistor instead of the standard LTPS results in a much lower off-state current compared to the standard LTPS AMOLED displays [5].

Figure 2.2: LTPO pixel circuit schematic [5].

### 2.2.3 Full Adder ALU

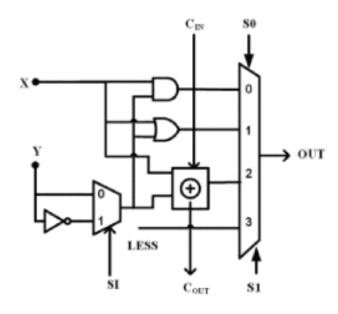

In 2022, researchers at the Chinese Academy of Sciences developed the first LTPO Arithmetic Logic Unit (ALU) [22]. The 1-bit ALU circuit contains the arithmetic operations ADD, SUB, logical operations AND and OR, and set less than (SLT). The proposed ALU circuit contains one AND gate, one OR gate, one full adder, one inverter, and two multiplexers as seen in Figure 2.3. The ALU operates on a 15 V supply voltage. The results show that the LTPO ALU has significantly lower rise and fall times (32 µs and 64 µs, respectively) and a smaller circuit area compared to other TFT-based ALUs.

Figure 2.3: Circuit diagram of 1-bit LTPO ALU [22].

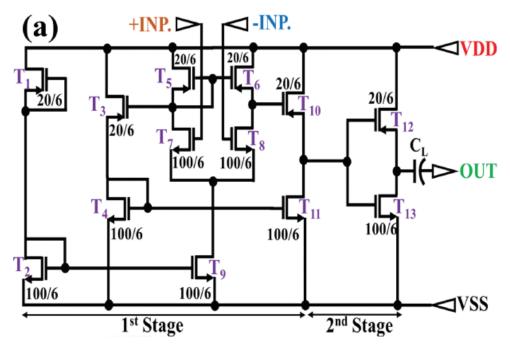

Figure 2.4: Schematic of the proposed two-stage LTPO op-amp, with the W/L ratio of each TFT in μm [13].

### 2.2.4 Operational Amplifier

Previous research on amplifiers based on LTPO TFT technology resulted in the two-stage single-ended operational amplifier (op-amp) shown in Figure 2.4. The circuit design consists of six p-type TFTs and seven n-type TFTs. The circuit can be divided into two stages. The first stage contains the input stage, current mirror, and the differential to single-ended converter stage. The second stage serves as an output buffer stage to improve the current drive capability.

This design achieves a voltage gain of 50.7 dB with a cut-off frequency of 200 kHz, and a unity gain bandwidth of 7 MHz. The op-amp operates on a ±20 V dual power supply and consumes 0.6 mW of power. The op-amp also exhibits a slew rate of 22.7 V/µs up and 6.4 V/µs down. These results prove that an LTPO TFT amplifier is capable of producing a high gain over a very large frequency range. However, this amplifier is not suitable for a wearable ECG AFE. The use of a high dual power supply is incompatible with typical wearable applications, which operate on a single, low-voltage supply (commonly 3 V or less) to ensure safety and energy efficiency [23]. Furthermore, both the amplifier's cut-off frequency and the slew rate far exceed the requirements for ECG signal processing. Reducing these specifications would lead to a more power-efficient and application-specific design without compromising the signal integrity.

## 2.3 AFE for ECG signals

ECG is the recording of electrical activity generated by the heart during each muscle contraction cycle. It is a widely used diagnostic tool for detecting and monitoring various cardiac conditions. With the increasing demand for smart healthcare solutions, significant research is already underway on developing a flexible wearable device to measure heart rate and ECG signals [4], [10], [24], [25].

Figure 2.5: Typical ECG signal cycle. a) a single ECG cycle, and b) ECG over a 10-second period. [26].

### 2.3.1 Measurement

Figure 2.5a shows an illustration of a single heartbeat cycle of the ECG with all major waveform components highlighted. Figure 2.5b shows the waveform diagram of an ECG recording over a 10-second interval, demonstrating noticeable variations between consecutive cycles. A typical ECG signal consists of a common-mode voltage of  $\sim 1.5$  V, with an additional direct current (DC) component of  $\pm 300$  mV and an average voltage amplitude of 2.5 mV, with occasional peaks of up to 5 mV [11]. Due to their low amplitude and susceptibility to various sources of noise, raw ECG signals require careful amplification and filtering before further processing. This task is performed by the AFE, which amplifies the signal while preserving signal integrity and suppressing noise.

From an engineering standpoint, the heart functions as a source of bio-electrical signals, while the body serves as the conductive path through which these signals propagate. These potential differences can be measured by placing two or more electrodes on the surface of the skin. The resulting signals are known as leads. Each lead provides a different projection of the electrical activity of the heart. Figure 2.6 illustrates a simplified example of the lead I measurement method, which measures the potential difference between the right arm (RA) and the left arm (LA). The resulting ECG signal can be derived as follows:

$$Lead I = LA - RA \tag{2.1}$$

### 2.3.2 Amplification Stage

Considering the amplifier stage, the American Health Association (AHA) recommends a bandwidth of 125 Hz for measuring ECG on adults [27]. The guidelines further specify that the amplitude response should remain flat to within  $\pm 0.5$  dB across the 0.1-30 Hz range, with the -3 dB cut-off frequencies no higher than 0.67 Hz at the low end and no lower than 150 Hz at the high end. [28] has established a standard bandwidth of 250 Hz for measuring ECG signals on children up to 16 years old. Any frequencies higher than this can be considered as noise and should be filtered out in the AFE.

Figure 2.6: Illustrations for a) the electrical signal of Lead I measurement and b) the placement of the electrodes in context for a smart plaster [10].

### 2.3.3 ADC

A typical AFE consists of a chain of instrumentation and/or operational amplifiers, followed by filtering stages and an ADC. The resulting output is a digital representation of the ECG waveform suitable for further interpretation and processing by an external system. All components preceding the ADC are designed to condition the signal to ensure it operates within its optimal range and captures the analogue signal as accurately as possible. An ADC's resolution refers to the smallest distinction in voltage it can detect. For example, on an 8-bit ADC, with a reference voltage  $(V_{ref})$  of 3 V (usually equal to the power supply voltage), the resolution is as follows:

Resolution =

$$\frac{V_{ref}}{2^N}$$

(2.2)

$$=\frac{3.00\ V}{2^8}=11.7\ mV\tag{2.3}$$

Note that this value already exceeds more than twice the maximum amplitude typically observed in ECG signals. As a result, this ADC is not suitable for directly processing a raw ECG input. To ensure accurate digitisation, the ADC resolution must increase significantly, or the input signal must be appropriately amplified to utilise the full dynamic range of the ADC.

These results suggest two viable design approaches for an AFE. The first involves employing a high-gain, low-noise analogue circuit that sufficiently amplifies the signal before digitisation with a lower-resolution ADC. Alternatively, a low-gain amplifier can be used in conjunction with a high-resolution ADC to capture the signal accurately without extensive amplification. Texas Instruments recommends an amplification of approximately 500x for a 16-bit ADC, or a 24-bit ADC for an amplification of approximately 5x [11]. Assuming a reference voltage of 3.00 V for both cases, this results in the following effective voltage resolutions:

Resolution<sub>16-bit</sub> =

$$\frac{3.00 \ V}{2^{16}} = 45.8 \ \mu V$$

(2.4)

Resolution<sub>24-bit</sub> =

$$\frac{3.00 \ V}{2^{24}} = 179 \ pV$$

(2.5)

If we now assume average voltage peaks of 2.5 mV, the amount of different data points between the common-mode voltage and the peak voltage, for an amplifier with an amplification of 500x with a 16-bit ADC and an amplifier with an amplification of 5x with a 24-bit ADC respectively, can be approximated with the following equation:

Data Points<sub>16-bit</sub> =

$$\frac{2.5 \ mV * 500}{45.8 \ \mu V} = 27,300$$

(2.6)

Data Points<sub>24-bit</sub> =

$$\frac{2.5 \ mV * 5}{179 \ pV} = 70,000$$

(2.7)

Although the second hypothetical AFE yields nearly three times as many potential data points as the first, both can be considered to operate within the same order of magnitude. Each is capable of delivering a high-quality digital output suitable for ECG signal processing. Ultimately, the choice between these designs depends on the trade-offs the design engineer is willing to make between performance requirements, power constraints, and cost in order to achieve the most optimal AFE implementation.

## Chapter 3

## Analogue Design Methodology

This chapter discusses and justifies the design choices made in the analogue amplifiers presented in this thesis to meet the requirements of an AFE for ECG signals.

## 3.1 Fully Differential and Single-Ended amplifiers

An operational amplifier that provides a single output referenced to ground is referred to as single-ended, whereas one that produces two complementary outputs is known as fully differential. A differential signal consists of two voltages with equal magnitude and frequency but opposite polarity. These signals can be characterized by two components: the common-mode voltage  $(V_{\rm CM})$ , which is the average of the two output voltages, and the differential-mode voltage  $(V_{\rm DM})$ , which is the difference between them.

The primary advantage of a fully differential output is its immunity to external noise sources that affect both signals equally. Consider the example of an amplifier with a supply noise in Figure 3.1. The noise generated by the supply voltage  $V_{\rm DD}$  affects both the single-ended output  $V_{\rm out}$  and the fully differential output signals  $V_{\rm X}$  and  $V_{\rm Y}$ . However, since the  $V_{\rm DD}$  noise appears as a common-mode component, it will be removed in  $V_{\rm DM}$ , which is equal to  $V_{\rm X}-V_{\rm Y}$ . ECG signal measurements will contain many of these types of external noise, not only from the supply voltage but also at the input nodes caused by the human body. In addition, since this specific amplifier will likely be placed close to the human skin, it will constantly be influenced by these external signals. All of these influences can be eliminated by implementing a differential output over a single-ended output.

An additional advantage of fully differential amplifiers is their greater signal swing. A single-ended output signal can swing from 0V to  $V_{\rm DD}$ , and a fully differential output allows each output node to swing over this same range in opposite directions. As a result, the total differential output swing can reach  $2V_{\rm DD}$ , doubling the available dynamic range.

## 3.2 Input differential pair

Figure 3.2 illustrates a basic common-source amplifier stage. It is referred to as "common-source" because the source terminal of the transistor serves as a shared reference point for both the input signal applied at the gate and the output signal taken from the drain. The amplification of a

Figure 3.1: Effect of supply noise on (a) a single-ended circuit and (b) a differential circuit.

Figure 3.2: Common-source input pair.

signal  $A_v$  is defined by the ratio between the change in the output signal  $\partial V_{out}$  and based on a change in the input signal  $\partial V_{in}$ . For ease of analysis, it is assumed that all transistors operate in the saturation region. This means that the voltage between the drain and the source  $V_{DS}$  is always higher than the voltage difference between the gate and the source  $V_{GS}$  and the threshold voltage of the transistor  $V_T$ .

$$A_v = \frac{\partial V_{out}}{\partial V_{in}} = \frac{\partial V_{DS}}{\partial V_{GS}} \tag{3.1}$$

Assuming there is no change in input voltage, no current will flow to the output and  $I_D = I_R$ . This means that:

$$V_{out} = V_{DD} - V_R = V_{DD} - I_D R (3.2)$$

The input signal  $V_{in}$  will be amplified to  $V_{out}$  by a factor of transconductance  $g_m$  of the transistor. This describes the change in current flowing through the transistor  $\partial I_D$  as a result of a change in gate-source voltage  $\partial V_{GS}$ .

$$g_m = \frac{\partial I_D}{\partial V_{GS}} \tag{3.3}$$

$$I_{D_{sat}} = \frac{1}{2}\mu C_{ox} \frac{W}{L} (V_{GS} - V_T)^2$$

(3.4)

Based on the equation for the drain current in a transistor in saturation 3.4, the following equation can be derived:

Figure 3.3: Input differential pair with resistive load.

$$g_m = \mu C_{ox} \frac{W}{L} (V_{GS} - V_T) \tag{3.5}$$

By inserting 3.4 into 3.2 we get:

$$V_{out} = V_{DD} - R \frac{1}{2} \mu C_{ox} \frac{W}{L} (V_{GS} - V_T)^2$$

(3.6)

Now, inserting this into 3.1 we get the following equation for the amplification of a simple common-source stage:

$$A_v = -R\mu C_{ox} \frac{W}{L} (V_{GS} - V_T) \tag{3.7}$$

$$= -g_m R (3.8)$$

Since the amplifier will contain a differential input signal and two output signals, the topology will need to have more than one input transistor. Figure 3.3 illustrates a typical input differential pair with a resistive load and a constant tail current source  $I_{SS}$ , which is always equal to  $i_{D1}+i_{D2}$ . This means that if  $V_{in1}=V_{in2}$  then  $i_{D1}=i_{D2}=i_{SS}/2$  and any change in  $i_{D1}+\Delta i$  results in an equal change  $i_{D1}-\Delta i$ . The output common mode voltage  $V_{OCM}$  is as follows:

$$V_{OCM} = V_{DD} - \frac{RI_D}{2} \tag{3.9}$$

### 3.3 Positive Channel Load

The circuit in Figure 3.3 makes use of resistors as load devices in the circuit. These show up in equation 3.8 as a defining factor for the gain. Another way of greatly increasing this gain is by replacing them with p-type transistors with a constant bias voltage  $V_B$  at their gate, as

Figure 3.4: Differential pair circuit with p-type load.

illustrated in Figure 3.4. By substituting the resistance in equation 3.1 by the transconductance, the total resistance at the output node  $V_{out+}$  now becomes equal to  $r_{O1}||r_{O3}$ , and we get the following:

$$A_v = -\frac{g_m}{r_{o,1}||r_{o,3}} \tag{3.10}$$

With  $r_{O1}$  and  $r_{O3}$  the output impedance of the respective transistors. In a transistor,  $V_{DS}$  and  $r_{O}$  are not as strongly related as the value of a resistor to its voltage drop. This means that impedance (and, in turn, gain) can be increased while maintaining a low voltage drop [29].

### 3.4 Slew Rate and Tail Current

The slew rate (SR) of an amplifier is the maximum speed at which it can change the output signal, expressed in  $V/\mu s$ . It essentially defines how quickly the output voltage can change in response to a change in input voltage. When a fast or large input step is applied in a non-ideal amplifier, the output cannot immediately follow. This can cause performance limitations and lower the signal integrity. The slew rate can be defined as follows:

$$SR = \max \left| \frac{dV_{\text{out}}}{dt} \right| \tag{3.11}$$

To measure the slew rate of an amplifier, a signal with an infinitely high  $\Delta V$ , also known as a step, is applied at the input (see Figure 3.5). The slew rate can be derived from  $\Delta V_{out}/\Delta t$  in the linear part of the rise time.

In a simple differential pair amplifier, the slew rate is defined as follows:

Figure 3.5: Slew rate example

$$SR = \frac{I_{ss}}{C_L} \tag{3.12}$$

where  $I_{ss}$  is the tail current and  $C_L$  is the load capacitance [29].

In summary, the slew rate defines how quickly an amplifier can change its output voltage in response to an input change, and while this is crucial in high-speed applications, it is unnecessary for ECG processing. Designing for a high slew rate based on 3.12 results in a higher current through the input transistors, which in turn increases the overall power consumption. Since an ECG amplifier does not require fast switching due to the low-frequency nature of the signal, prioritising a high slew rate offers no practical advantage. Therefore, a low tail current is selected to support a low-power design that remains sufficient for the intended application. According to established guidelines, ECG AFEs should achieve a minimum slew rate of  $400 \, \mu V/ms$  [30].

## 3.5 Cut-off frequency and phase margin

The cut-off frequency,  $f_c$  or  $f_{-3dB}$ , of an amplifier is the point where its gain falls 3 dB below the low-frequency gain. It is essentially considered the highest frequency where the amplifier still provides an acceptable amplification compared to its low-frequency behaviour. As previously mentioned, standard ECG signals do not contain any significantly high frequency signals. This means the amplifier can be designed for a low cut-off frequency, and as a result also function as a low-pass filter.

When negative feedback is applied to an amplifier, the system's stability depends on maintaining a sufficient phase margin. If the phase shift  $\varphi$  reaches  $-180^{\circ}$  at a frequency where the gain is still above 0 dB, the negative feedback effectively becomes positive feedback with  $0^{\circ}$  phase shift, resulting in oscillation. Each pole in an amplifier introduces a  $90^{\circ}$  phase lag into the system [29]. Therefore, in systems with more than one pole, the total phase shift can approach or exceed  $-180^{\circ}$ , especially at higher frequencies. In an ideal system without variability, it is sufficient to ensure that the amplifier phase surpasses  $0^{\circ}$  after the amplification drops below 0 dB. However, in real-world implementations, process variations and non-idealities can cause both the gain and phase to deviate from their ideal values. The phase margin represents the allowable deviation in phase before the system reaches instability, providing a buffer that ensures a stable operation

Figure 3.6: Simple NMOS current mirror.

under non-ideal conditions.

$$PM = \varphi - (-180^\circ) \tag{3.13}$$

Analogue design engineers usually opt for a phase margin of approximately 60°. However, any phase margin larger than 45° is generally acceptable [31]. If the phase margin falls below this value, the risk of oscillating on a negative feedback system will be too high.

### 3.6 Current Mirror Design

Referring back to Figure 3.3, the circuit contains a tail current source  $I_{SS}$  that keeps a constant current flowing between the sources of M1 and M2 and the ground. This constant current source is typically implemented using a current mirror that copies a constant independent reference current. In this context, a basic NMOS current mirror can be employed, as shown in Figure 3.6, where transistors M8 and M9 form a simple current mirror structure.

If both transistors operate in the saturation region, and by applying equation 3.4, the drain currents of the reference and output transistors can be expressed as:

$$I_{ref} = \frac{1}{2}\mu C_{ox} \left(\frac{W}{L}\right)_1 (V_{GS} - V_T)^2$$

(3.14)

$$I_{out} = \frac{1}{2}\mu C_{ox} \left(\frac{W}{L}\right)_2 (V_{GS} - V_T)^2$$

(3.15)

$$I_{out} = \frac{(W/L)_2}{(W/L)_1} I_{ref} \tag{3.16}$$

This shows that the output current is a scaled version of the reference current, where the scaling factor is determined by the ratio of the channel dimensions (W/L). Thus, if transistors M1 and M2 are identically sized, then the currents are also equal  $(I_{ref} = I_{out})$  [29], [32].

#### Cascoding 3.7

As demonstrated in equation 3.10, increasing the output impedance directly increases the gain of the amplifier. One widely used method to achieve this is through cascode configurations. In a cascode structure, an additional transistor is stacked above the amplifying transistor, effectively increasing the output resistance by minimising the effect of channel length modulation.

This configuration not only improves gain, but also enhances bandwidth and reduces the Miller effect. Figure 3.7 illustrates a standard common source stage with a cascode transistor.

The gain of a cascoded amplifier stage can be approximated as follows:

$$A_v = \frac{\partial V_{DS}}{\partial V_{GS}} = \frac{\partial I}{\partial V_{in}} \frac{\partial V_{out}}{\partial I} = \frac{-g_{m1}}{g_{tot}}$$

(3.17)

(3.18)

$$g_{tot} = g_L + g_{out} = g_L + \frac{g_{o1}g_{o2}}{g_{o1} + g_{o2} + g_{m2}}$$

(3.19)

After inserting 3.19 into 3.18 and assuming  $g_L \approx 0$  and  $g_{m1}$  and  $g_{m2} >> g_{o1}$  and  $g_{o1}$ :

$$A_{v} \approx \frac{g_{m1}(g_{o1} + g_{o2} + g_{m1})}{g_{o1}g_{o2}}$$

$$\approx \frac{g_{m1}g_{m2}}{g_{o1}g_{o2}}$$

(3.20)

$$\approx \frac{g_{m1}g_{m2}}{g_{o1}g_{o2}} \tag{3.21}$$

Optimizing a cascode stage results in a large voltage gain over the cascode transistor's  $V_{DS}$  and a lower gain over the input transistor's  $V_{GS}$ , resulting in a lower input capacitance  $C_{in}$ , also known as the Miller effect [33].

#### Two-Stage Amplifier 3.8

Two-stage amplifier configurations are commonly used to achieve higher overall gain and improved output performance. The first stage is typically optimised for maximum voltage gain and consists of a differential pair with high transconductance, as seen previously. The second stage is designed to provide a large output voltage swing and sufficient drive capability for the subsequent load.

This second stage usually consists a p-type common source transistor acting as a current source, biased with a constant gate voltage. The bias current of this stage is generally higher than the tail current of the first stage, allowing for greater drive strength. As shown in Figure 3.8, the second stage typically does not include cascode devices, prioritising output swing over gain enhancement.

Figure 3.7: Common source stage with a cascode transistor.

Figure 3.8: Typical two stage amplifier circuit. [29]

### 3.9 Common Mode Rejection Ratio

As explained before in section 3.1, the signal at the two input nodes will contain a common-mode and a differential-mode signal ( $V_{ICM}$  and  $V_{IDM}$ ). An ideal fully differential amplifier will only amplify the difference between the two input nodes, which is  $V_{IDM}$ . Any non-ideal amplifier contains an undesirable differential component that is produced by the variations in  $V_{ICM}$ . This component is quantified by the common-mode rejection ratio (CMRR), which is defined as the ratio of the differential gain to the common-mode gain, defined in decibels (dB). In other words, it measures how well the amplifier amplifies the desired differential signal while rejecting the undesired common-mode signals [29].

$$CMRR = 20\log_{10}\left(\frac{A_{\text{diff}}}{A_{\text{cm}}}\right) \tag{3.22}$$

Recommendations typically range from 85 to 120 dB [34], [35], [36]. In practice, CMRR is strongly affected by mismatches in transistor fabrication. An ideal fully differential amplifier with perfectly matched transistors would achieve an infinite CMRR. However, since this work is based exclusively on simulations under idealised conditions, the reported CMRR values will not be representative of a real-world implementation.

## Chapter 4

## Results and Discussion

#### 4.1 Simulation Models

The research facility ES&S provided two different simulation models for the p-type and n-type LTPO TFTs. The first simulation model is based on an existing fabrication of LTPO. The second is based on realistic results of p-type LTPS and n-type a-IGZO TFTs, but has never been fabricated yet. This means that the performance of the second simulation model is only speculation. The first amplifier discussed in the following chapter is developed based on these first simulation models, and all the latter are based on the second simulation models.

### 4.2 Simulation Setup

All circuit characterisation was performed using the Cadence Virtuoso Spectre simulation environment. These simulations were designed to evaluate the amplifier's performance in both the frequency and time domains.

The frequency domain analysis is visualised through a bode plot, which highlights two primary performance metrics:

- Magnitude Response: The absolute gain of the amplifier expressed in decibels (dB) over a range of frequencies.

- Phase Response: The phase shift between the input and output signals, expressed in degrees (°), as a function of frequency.

The time domain performance was evaluated via transient simulations, providing the following information:

- Output Waveform: The time domain response of the amplifier output when subjected to an ECG input signal.

- **Signal Integrity:** Observations of how accurately the output replicates the input waveform, including any delay, distortion, or noise.

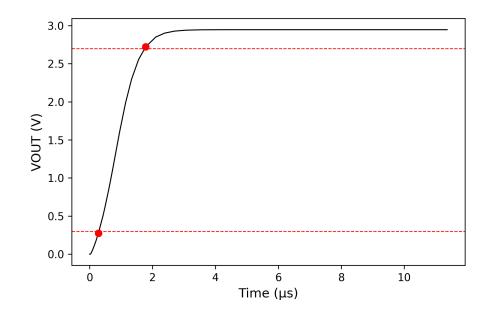

Additionally, the slew rate is determined by sending an impulse waveform at the positive input node and measuring the slope at the output.

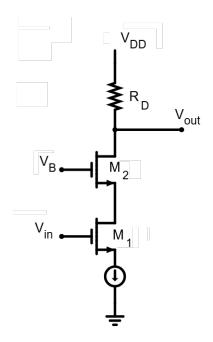

Figure 4.1: Two-stage amplifier in LTPO.

### 4.3 Simple Two-Stage amplifier

#### 4.3.1 Circuit Design

Figure 4.1 illustrates the circuit schematic of the two-stage amplifier in LTPO. The amplifier contains four p-type TFTs and six n-type TFTs and can be subdivided into three parts:

- M0,M1,M2,M3: a differential pair input stage in common source configuration with a p-type load.

- M4,M5: a current mirror serving as an ideal current source.

- M6,M7,M8,M9: a common drain output stage.

The TFT dimensions and biasings are given in Table 4.1.

Transistors M0 and M1 recieve the input signals  $V_{in+}$  and  $V_{in-}$  respectively at their gates. Transistors M2 and M3 serve as p-type loads to increase the output impedance of the first stage. An ideal current source  $I_{bias}$  provides a constant current at the drain of M4 that is mirrored by M5 at the drain to produce a constant tail current. The p-type TFTs M6 and M7 at the second stage are placed in common drain configuration and amplify the signal a second time with higher driving capability. N-type transistors M8 and M9 serve as ideal current sources at the output stage.

Table 4.1: TFT dimensions and bias parameters of the amplifier of the two stage amplifier.

| Transistor | Width [µm] | Length [µm] | Multiplier | Bias       | Voltage [V] | Current [nA] |

|------------|------------|-------------|------------|------------|-------------|--------------|

| M0, M1     | 160.0      | 4.0         | 1          | $V_{B1}$   | -5.0        |              |

| M2, M3     | 5.0        | 40.0        | 1          | $V_{B2}$   | 4.0         |              |

| M4, M5     | 160.0      | 0.8         | 16         | $I_{bias}$ |             | 500          |

| M6, M7     | 20.0       | 6.0         | 1          |            |             |              |

| M8, M9     | 20.0       | 6.0         | 1          |            |             |              |

Figure 4.2: Open loop test bench used for the two stage amplifier.

#### 4.3.2 Test Bench and Simulation Results

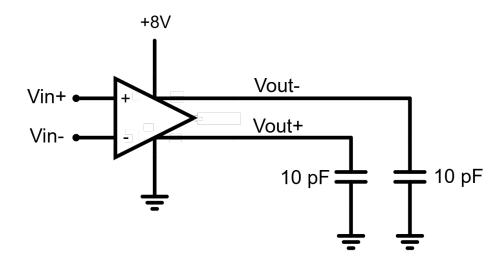

Figure 4.2 illustrates the test bench configuration used to characterise the open-loop gain, phase response, and transient behaviour. The amplifier operates on an 8 V supply voltage  $(V_{DD})$ . The input signals  $(V_{in+} \text{ and } V_{in-})$  are simulated representations of realistic positive and negative lead I ECG waveforms with a common-mode voltage of 4 V, corresponding to the midpoint between ground and  $V_{DD}$ . The amplifier is designed to drive a capacitive load of 10 pF at each output node.

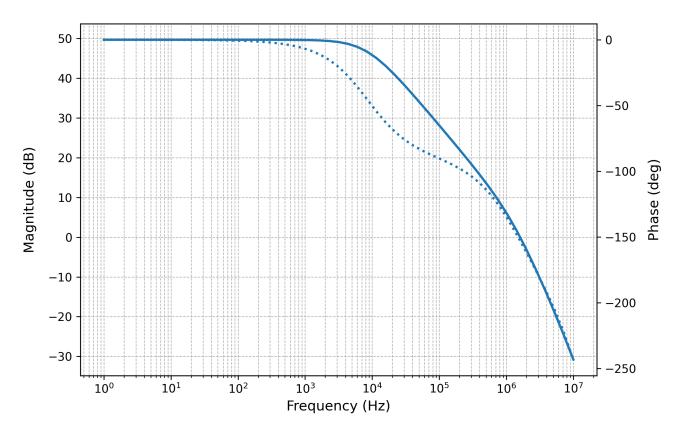

Figure 4.3 displays the open-loop gain and phase shift of the output signal in a bode plot. The gain after the first amplification stage reaches 14.4 dB. The total low-frequency open-loop gain after the second stage is 33 dB. The -3 dB cut-off frequency is 610 Hz and the unitive gain bandwidth (UGBW) is 29 kHz. This results in a phase margin of 94°. The slew rate is equal to 175 V/ms and is illustrated in Figure 4.5.

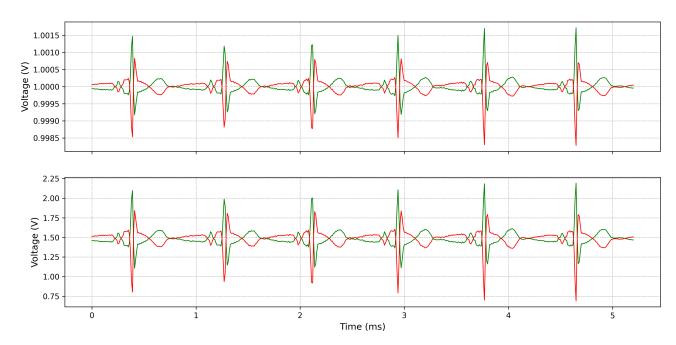

The transient response is shown in Figure 4.4, where the output signals operate around a common-mode voltage  $V_{OCM}$  of 3.5 V. The waveform in the transient response demonstrates excellent signal integrity of the ECG waveform at the output while amplifying the signal with a magnitude of approximately 45. A summary of the amplifier's performance parameters is provided in Table 4.2.

Figure 4.3: Bode plot of the open loop gain (solid line) and phase delay (dotted line) of the two stage amplifier.

Figure 4.4: Transient response of the input (top) and output (bottom) signal of the two stage amplifier, with the positive nodes in green and negative nodes in red.

Figure 4.5: Slew rate of the two stage amplifier.

Table 4.2: Performance parameters of the two stage amplifier.

| Parameter                   | Value |

|-----------------------------|-------|

| Open-loop gain (dB)         | 33    |

| $f_{cut-off}$ (Hz)          | 600   |

| UGBW (kHz)                  | 29.2  |

| PM (°)                      | 93    |

| $V_{OCM}$ (V)               | 3.5   |

| Power (µW)                  | 7.34  |

| SR (V/µs)                   | 0.175 |

| Approx. $V_{peak,AVG}$ (mV) | 70    |

#### 4.3.3 Discussion

The results at the output nodes of this amplifier are not sufficient for the requirements set. Mainly, the amplifier cannot provide enough open loop gain to achieve a reasonable resolution for a 16-bit ADC with a resolution of 122  $\mu$ V when  $V_{ref}$  is equal to  $V_{DD}$  (8 V). This results in approximately 600 distinguishable data points between  $V_{OCM}$  and  $V_{peak,AVG}$ , failing to meet the amplification guidelines recommended by Texas Instruments (see Chapter 2). This low amplification, especially after the first stage, can be explained by the very low transconductance  $(g_m)$  of the n-type TFTs (see Chapter 3).

However, ignoring this lack of amplification, this amplifier proves to be very reliable. The phase margin of  $93^{\circ}$  ensures high stability even with a large system variability. The slew rate of 175 V/ms is more than sufficient for this application. Additionally, the cut-off frequency of 600 Hz and the UGBW of 29.2 kHz already provide a level of filtering on high-frequency noise without any active filters present. However, considering the very low average power consumption of 7.34  $\mu$ W, this amplifier could still be viable in combination with a higher resolution ADC that consumes more power.

## 4.4 Current Mirror Based Amplifier

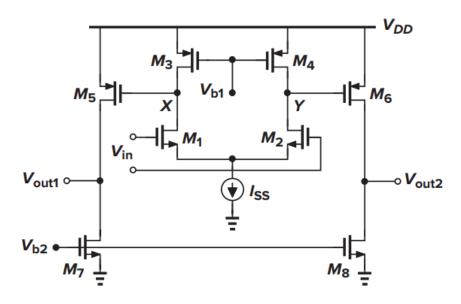

#### 4.4.1 Circuit Design

Figure 4.6 illustrates the circuit schematic of an amplifier based on current mirror amplification. The amplifier consists of six p-type TFTs and ten n-type TFTs and can once again be subdivided into multiple parts:

- M0, M1: a differential pair input stage in common source configuration.

- M2, M3: a current mirror serving as an ideal tail current source.

- M4, M5, M6, M7: cascode transistors used to increase the output impedance in the first stage.

- M8, M9, M10, M11: p-type transistors in current mirror configuration.

- M12, M13, M14, M15: an n-type current mirror that serves as an ideal current source in the output stage.

The dimensions and biases of the TFT are given in Table 4.3.

Transistors M0 and M1 receive the input signals ( $V_{in+}$  and  $V_{in-}$ ) at their respective gates. The ideal current source  $I_{B1}$  provides a constant current at the drain of M2 that is mirrored by M3 at the drain to produce a constant tail current. The n-type TFTs M4 and M5 and the p-type TFTs M6 and M7 are cascode transistors with a constant bias voltage at their gates to increase the output impedance of the first stage. The p-type transistors M8 to M11 form a current mirror configuration with deliberately chosen mismatched W/L ratios. This configuration scales the current flowing into the reference branch and replicates a proportionally larger current in the output branch. The remaining transistors M12 until M15, also in current mirror configuration, provide a constant current source at the output node.

Figure 4.6: Circuit diagram of a current mirror based amplifier.

#### 4.4.2 Test Bench and Simulation Results

Figure 4.7 illustrates the test bench configuration used to characterise the open-loop gain, phase response, and transient behaviour of the amplifier. The amplifier operates on a 3.00 V supply voltage  $(V_{DD})$ . The input signals  $V_{in+}$  and  $V_{in-}$  are simulated representations of realistic positive and negative Lead I ECG waveforms, with a common-mode voltage of 1.00 V. The amplifier is designed to drive a capacitive load of 10 pF at each output node.

Figure 4.8 displays the open-loop gain and phase shift of the output signal in a bode plot. The total low-frequency open-loop gain is 36.5 dB. The -3 dB cut-off frequency is 10.3 kHz and the UGBW is 700 kHz. This results in a phase margin of 67°.

The transient response is illustrated in Figure 4.9, where the output signals operate around a common-mode voltage  $V_{OCM}$  of 1.0 V. The waveform in the transient response demonstrates excellent signal integrity of the ECG waveform at the output while amplifying the signal with a magnitude of approximately 63x. A summary of the amplifier's performance parameters is provided in Table 4.4.

#### 4.4.3 Discussion

Once again, this amplifier does not achieve the gain requirements set in order to achieve a sufficient amount of data points for a 16-bit ADC, with a resolution of 45.8  $\mu$ V. This results in approximately 3,000 distinguishable data points between  $V_{OCM}$  and  $V_{peak,AVG}$ , which is again not enough for the recommended resolution by Texas Instruments (see Chapter 2).

Figure 4.7: Open loop test bench of the current mirror amplifier.

Figure 4.8: Bode plot of the open loop gain (solid line) and phase delay (dotted line) of the current mirror amplifier.

Table 4.3: TFT dimension and bias parameters of the current mirror amplifier.

| Transistor | Width [µm] | Length [µm] | Multiplier | Bias     | Voltage [V] | Current [µA] |

|------------|------------|-------------|------------|----------|-------------|--------------|

| M0, M1     | 30.0       | 1.2         | 4          | $V_{B1}$ | 2.0         |              |

| M2, M3     | 24.0       | 1.2         | 1          | $V_{B2}$ | 1.5         |              |

| M4, M5     | 5.0        | 0.8         | 1          | $I_{B1}$ |             | 0.60         |

| M6, M7     | 1.0        | 0.8         | 1          | $I_{B2}$ |             | 1.00         |

| M8, M9     | 2.4        | 1.2         | 1          | $I_{B3}$ |             | 1.00         |

| M10, M11   | 6.0        | 1.2         | 2          |          |             |              |

| M12, M13   | 2.0        | 0.8         | 1          |          |             |              |

| M14, M15   | 2.0        | 0.8         | 2          |          |             |              |

Figure 4.9: Transient response of the input (top) and output (bottom) signal of the current mirror amplifier, with the positive nodes in green and negative nodes in red.

However, ignoring this lack of amplification, this amplifier is shown to be very reliable with a phase margin of  $67^{\circ}$ . The high cut-off frequency of 10.3 kHz and the UGBW of 700 kHz indicate sufficient bandwidth headroom to accommodate an additional (third) amplification stage while still meeting minimum frequency requirements. This amplifier also consumes an average power of  $8.63~\mu W$  when operating from a 3.00~V power supply, which aligns more with the low-power requirements typical for wearable and battery-powered ECG applications.

Table 4.4: Performance parameters of the current mirror amplifier.

| Parameter                   | Value |

|-----------------------------|-------|

| Open-loop gain (dB)         | 36    |

| f cut-off (Hz)              | 10.3k |

| UGBW (kHz)                  | 700   |

| PM (°)                      | 67    |

| $V_{OCM}$ (V)               | 1.0   |

| POWER (µW)                  | 8.63  |

| SR (V/µs)                   | -     |

| Approx. $V_{peak,AVG}$ (mV) | 140   |

## 4.5 High Gain Two Stage Amplifier

#### 4.5.1 Circuit Design

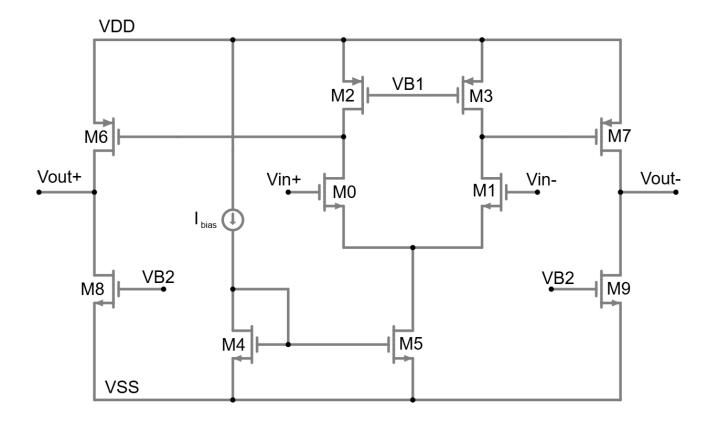

Figure 4.10 illustrates the circuit schematic of a two-stage cascode amplifier. The amplifier consists of four p-type TFTs and ten n-type TFTs and can once again be subdivided into multiple parts:

- M0, M1: a differential pair input stage in common source configuration.

- M2, M3: p-type load transistors to increase the output impedance in the first stage.

- M4, M5: a current mirror serving as an ideal tail current source.

- M6, M7: n-type cascode transistors used to increase the output impedance in the first stage.

- M8, M9: p-type transistors in the output stage in common drain configuration.

- M10, M11, M12, M13: an n-type current mirror that serves as an ideal current source in the output stage.

The TFT dimensions and biasings are shown in Table 4.5.

Transistors M0 and M1 receive the input signals ( $V_{in+}$  and  $V_{in-}$ ) at their respective gates. M2 and M3 are p-type load transistors in the differential pair stage. The ideal current source  $I_{B1}$  provides a constant current at the drain of M4 that is mirrored by M5 at the drain to produce a constant tail current. The n-type TFTs M6 and M7 and are cascode transistors with a constant bias voltage at their gates to increase the output impedance of the first stage. The p-type TFTs M6 and M7 in common drain configuration amplify the signal in the second stage. The remaining transistors M10 until M13 form a constant drive of current in the output stage as a current mirror with mismatched W/L ratios.

#### 4.5.2 Test Bench and Simulation Results

This amplifier operates on the same 3.00 V supply as the previous design and is intended for identical conditions, including a 1.00 V input common-mode voltage and a 10 pF load capacitance.

Figure 4.10: Circuit diagram the high gain two stage amplifier.

| TD 11 4 F  |               | 1           | 1 1 | 1 •  | 1          | C 1     | 4       | •         | 1.0       |

|------------|---------------|-------------|-----|------|------------|---------|---------|-----------|-----------|

| Table /Lb. | . I . H., I . | dimension   | and | hiac | parameters | of the  | current | mirror    | amplifier |

| Table 4.0. | T T T         | difficusion | and | DIGO | parameters | OI UIIC | Current | 111111101 | ampinioi. |

|            |               |             |     |      |            |         |         |           |           |

| Transistor | Width [µm] | Length [µm] | Multiplier | Bias     | Voltage [V] | Current [µA] |

|------------|------------|-------------|------------|----------|-------------|--------------|

| M0, M1     | 6.0        | 1.2         | 1          | $V_{B1}$ | 2.3         |              |

| M2, M3     | 2.0        | 0.8         | 1          | $V_{B2}$ | 2.0         |              |

| M4, M5     | 24.0       | 1.2         | 1          | $I_{B1}$ |             | 0.60         |

| M6, M7     | 6.0        | 1.2         | 1          | $I_{B2}$ |             | 1.00         |

| M8, M9     | 1.0        | 1.1         | 1          | $I_{B3}$ |             | 1.00         |

| M10, M11   | 18.0       | 1.2         | 2          |          |             |              |

| M12, M13   | 13.0       | 0.8         | 2          |          |             |              |

As a result, the same test bench setup is used to simulate its open-loop characteristics (see Figure 4.7).

Figure 4.11 displays the open-loop gain and phase shift of the output signal in a bode plot. The total low-frequency open loop gain is equal to 53.0 dB. The -3 dB cut-off frequency is 5.7 kHz and the UGBW is 1.6 MHz. The phase margin is equal to 30°.

The transient response is illustrated in Figure 4.12, where the output signals operate around a common-mode voltage  $V_{OCM}$  of 1.5 V. The waveform in the transient response demonstrates excellent signal integrity of the ECG waveform at the output while amplifying the signal with a magnitude of approximately 450x.

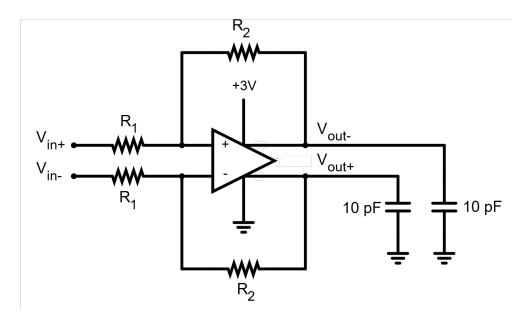

Figure 4.13 illustrates the amplifier with the addition of a negative feedback loop to the circuit. The feedback resistors R1 and R2 are 100 k $\Omega$  and 100 M $\Omega$ , respectively. The bode plot with closed-loop gain and phase shift is shown in Figure 4.14. This results in a closed-loop low

Figure 4.11: Bode plot of the open loop gain (solid line) and phase delay (dotted line) of the high gain two stage amplifier.

frequency gain of 49.6 dB, a -3 dB cut-off frequency of 8.5 kHz, a UGBW of 1.6 MHz, and a phase margin of 30°. A total summary of the amplifier's performance parameters in open and closed loop is provided in Table 4.6.

#### 4.5.3 Discussion

Compared to the previous two designs, this amplifier demonstrates significantly superior performance. With an open-loop gain of 53 dB and a cut-off frequency of 5.7 kHz, it successfully amplifies the full spectrum of ECG signals with high signal integrity. Notably, it also achieves the lowest power consumption among all designs, operating at 6.4  $\mu$ W on a 3 V power supply. The only limitation is the relatively low phase margin of 30°, which could affect stability under certain conditions.

Table 4.6: Performance parameters of the high gain two stage amplifier.

| Parameter                  | Open Loop | Closed Loop |

|----------------------------|-----------|-------------|

| Gain (dB)                  | 53.0      | 49.6        |

| $f_{cut-off}$ (kHz)        | 5.7       | 8.5         |

| UGBW (MHz)                 | 1.6       | 1.6         |

| PM (°)                     | 30        | 30          |

| $V_{OCM}$ (V)              | 1.5       | 1.5         |

| Power (µW)                 | 6.4       | 6.4         |

| SR (V/µs)                  | 1.64      | 1.64        |

| Approx. $V_{peak,AVG}$ (V) | 0.70      | 0.50        |

Figure 4.12: Transient response of the input and output (top) and output (bottom) signal of the high gain two stage amplifier, with the positive nodes in green and negative nodes in red.

Figure 4.13: Test bench for the high gain two stage amplifier with negative feedback.

Figure 4.14: Bode plot of the closed loop gain (solid line) and phase delay (dotted line) of the high gain two stage amplifier.

Figure 4.15: Slew rate simulation of the high gain two stage amplifier.

Figure 4.16: Output voltage signals of the AFE. Top: positive (green) and negative (red) output voltages, and the reference voltage (blue). Bottom: digital heartbeat pulse.

Upon introducing negative feedback, the amplifier's closed-loop gain is reduced to 49.6 dB. This results in an increase in cut-off frequency to 8.5 kHz, allowing more bandwidth. The phase margin stays the same at 30°. The lowering of the gain has caused an increase in bandwidth, enhancing overall stability and tolerance to system variability by making the low-frequency gain less dependent on the TFT's transconductance.

When this amplifier with negative feedback is paired with a 16-bit ADC (resolution: 45.8  $\mu$ V), voltage peaks of approximately 0.50 V from  $V_{OCM}$  to  $V_{peak,AVG}$  would result in around 11,000 distinguishable digital levels. These results show that this analogue amplifier can come within the same order of the recommended standard set by [11] (see Section 2.3.3).

## 4.6 Digital Signal Processing Unit

Typical AFEs incorporate a complete ADC that converts the analogue signal into a continuous stream of digital bits at the output. In its simplest form, such as a flash ADC [37], the architecture consists of an array of comparators with reference voltages that range from the lowest to the highest measurable voltage. The ADC first samples the analogue signal at fixed time intervals, defined by a constant sampling frequency. Each sampled value (still analogue) is then quantised to the nearest discrete level, as determined by the resolution of the ADC. Finally, this quantised level is encoded into its corresponding digital representation [38].

The digital component of the AFE in this thesis essentially compromises itself to a single comparator level of such a flash ADC. It compares the positive output node of the analogue amplifier with a single constant reference voltage, specifically chosen so that the signal only exceeds this value once every cycle, which is during the R wave peak of the ECG. The end result is a signal that returns a digital '1' once every heartbeat cycle, as can be seen in Figure 4.16. All transistor gates in the digital component of the AFE have a width of 1 µm and a length of 800 nm.

Figure 4.17: StrongARM latch (a) circuit and (b) its equivalent circuit in the reset stage. [40]

#### 4.6.1 StrongARM Latch